因為專業(yè)

所以領先

1、 2.5D/3D封裝:多層芯片堆疊,AI驅動下HBM需求大增,CoWoS產(chǎn)能成為算力關鍵卡口

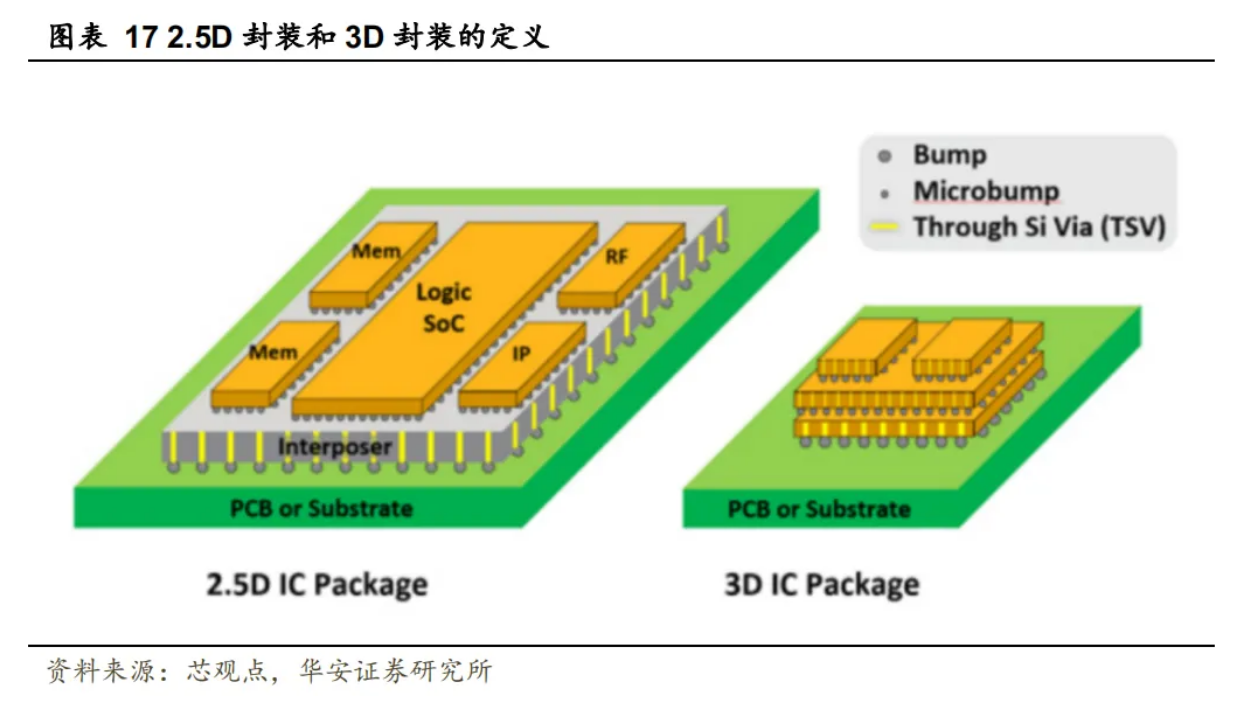

2.5D封裝和3D封裝的區(qū)別在于是否有硅中階層(Si Interposer)。在2.5D封裝中,所有芯片和被動元器件均在基板平面上方,至少有部分芯片和被動元器件安裝在中介層上,中介層通常作為一個載體,承載著各種電路組件和接口。而3D封裝舍棄中介層,直接在芯片上打孔和布線,電氣連接上下層芯片。所有芯片和被動元器件器件均位于基板平面上方,芯片堆疊在一起,在基板平面的上方有穿過芯片的硅通孔(TSV),在基板平面的下方有基板的布線和過孔。

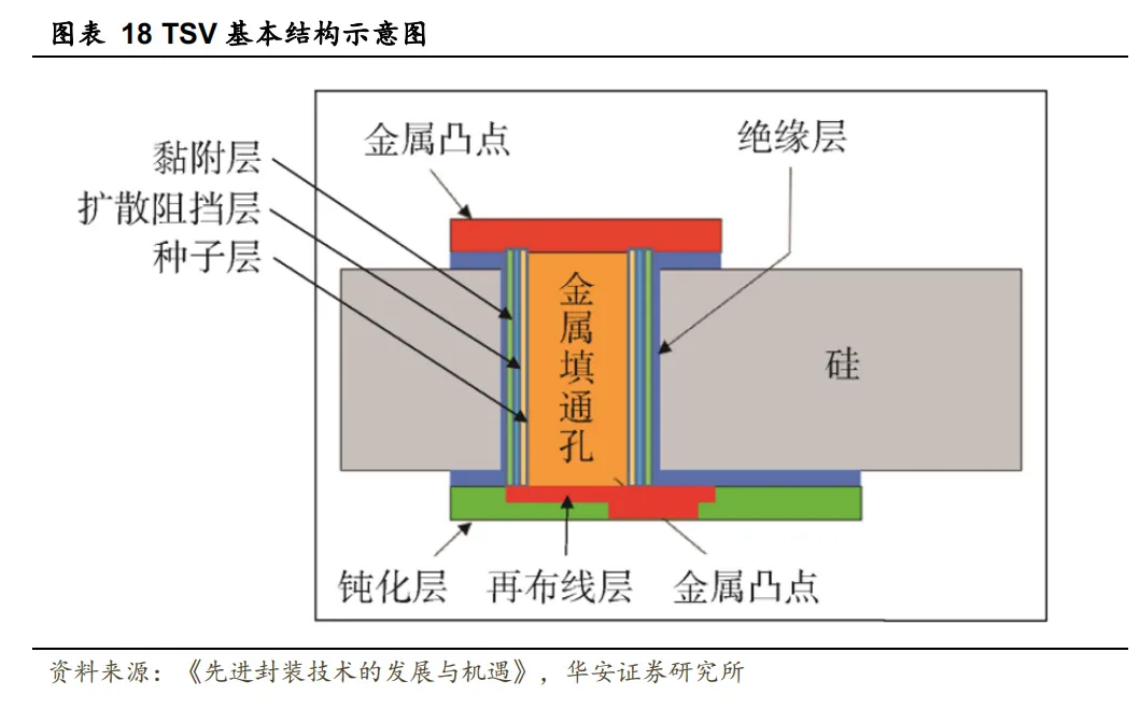

2.5D/3D封裝的關鍵工藝是硅通孔技術(through silicon via, TSV)。TSV是一種垂直互連技術,其概念由威廉·肖克利于1958年首次提出,是指連接硅晶圓兩面并與硅襯底以及其他通孔絕緣的電互連結構。TSV的尺寸通常在10μm×100μm和30μm×200μm之間,開口率介于0.1%~1%。與傳統(tǒng)平面互連相比,TSV能夠縮短互連長度、減小信號延遲、降低寄生電容和電感,實現(xiàn)芯片間低功耗和高速通信,同時增加寬帶并實現(xiàn)封裝的小型化。TSV目前主要應用于芯片三維堆疊、硅轉接板等領域。硅轉接板是芯片和有機基板的中間層,分為無源和有源兩類,其中無源轉接板僅包含金屬互連層,而有源轉接板則可集成供電、片內(nèi)網(wǎng)絡通信等功能。

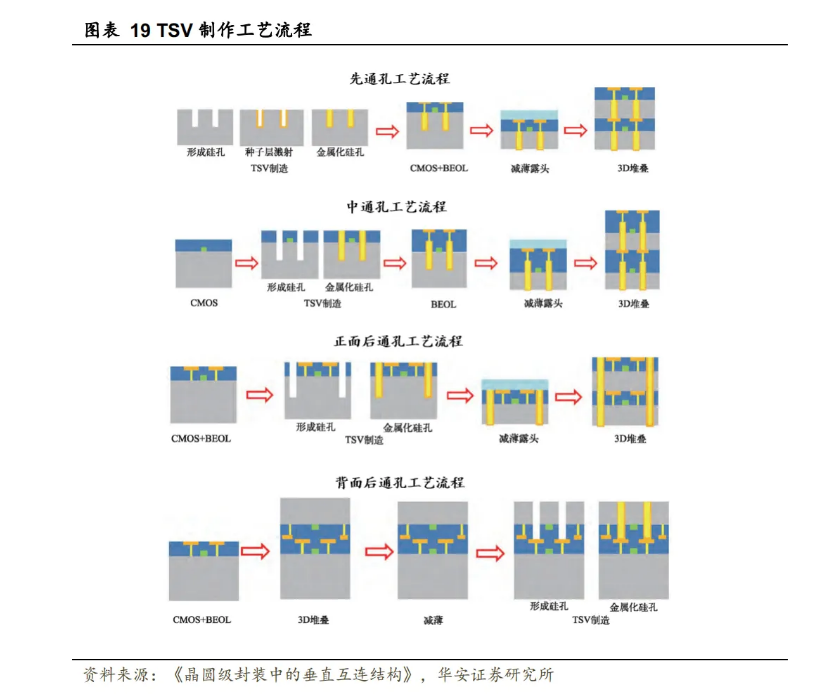

根據(jù)TSV被制作的時間順序,有3種類型的TSV工藝。分為先通孔工藝(Via First)、中通孔工藝(Via Middle)和后通孔工藝(Via Last),分別指TSV制作在晶圓制作工藝中的前、中或后段。

Via First是指在器件(如MOSFET器件)結構制造之前,先進行TSV結構的通孔刻蝕,孔內(nèi)沉積高溫電介質(zhì)(熱氧沉積或化學氣相沉積),然后填充摻雜的多晶硅。多余的多晶硅通過CMP去除。

Via Middle常常指在形成器件之后但在制造疊層之前制造的通孔工藝。在有源器件制程之后形成TSV結構,然后內(nèi)部沉積電介質(zhì)。淀積阻擋層鈦金屬和銅種子層,然后電鍍銅填充通孔,或通過化學氣相沉積鎢金屬填充通孔。

Via Last包括兩種工藝。正面后通孔工藝是在Back End of Line(BEOL)工藝處理結束后,從晶圓正面形成通孔的一種制造工藝。從概念上講,在晶圓上制造的后通孔工藝與中通孔工藝相似,但是對工藝溫度有進一步的限制(必須小于400℃)。背面后通孔工藝是在BEOL工藝處理結束后,從晶圓背面進行通孔結構的一種制造工藝。首先使用粘合劑將兩個器件晶圓以面對面方式粘合,接下來,將頂部晶圓減薄,將TSV結構刻蝕至頂部晶圓和底部晶圓上的焊盤,孔內(nèi)沉積電介質(zhì),最后,將金屬沉積到TSV結構中并進行表面金屬層再布線。

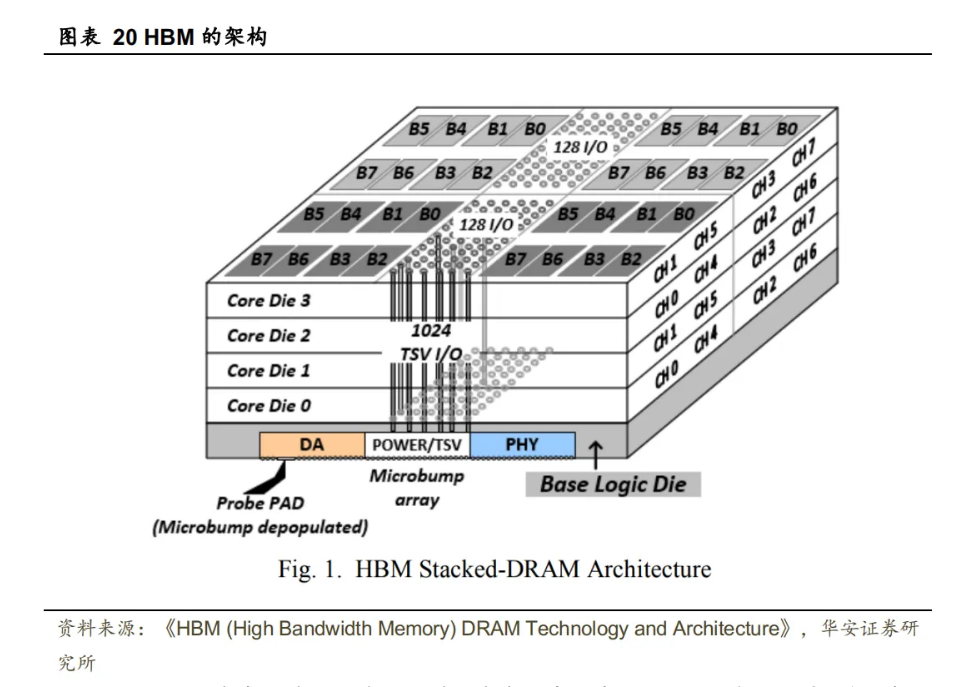

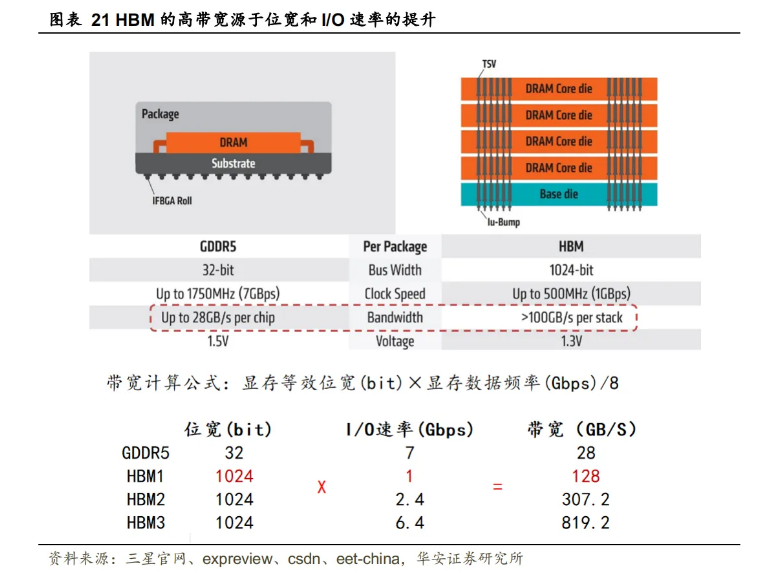

HBM使用2.5D/3D封裝技術打破“內(nèi)存墻”制約,成為AI及高性能計算需求下的主流方案。高帶寬內(nèi)存(High Bandwidth Memory, HBM)通過邏輯芯片和多層的DRAM堆疊來實現(xiàn)高速數(shù)據(jù)傳輸,突破了帶寬瓶頸,成為AI訓練芯片的首選。第一代HBM的架構如下圖所示,由4層DRAM和邏輯芯片堆疊在一起,每層之間通過TSV和微凸點連接。每個HBM有8個通道,每個通道有128個I/O,因此每個HBM有1024個I/O,即合計1024個TSV位于HBM的中間區(qū)域。存儲器和處理器通過無源轉接板上的再布線層(RDL)將HBM邏輯芯片的端口物理層(Port Physical Layer, PHY)與處理器的PHY相連。HBM的性能較傳統(tǒng)GDDR5更具優(yōu)勢,GDDR5的帶寬最高可達32 GB/s,而HBM1、HBM2和HBM2的帶寬分別達到了128 GB/s、307 GB/s和819 GB/s。其中,HBM內(nèi)部的DRAM堆疊屬于3D封裝,而HBM與芯片其他部分合封于硅中介層上屬于2.5D封裝。

HBM的帶寬提升源于堆棧式封裝帶來的高位寬以及I/O速率的提升。1)位寬:HBM的位寬是GDDR5的32倍。顯存帶寬是指顯示芯片與顯存之間的數(shù)據(jù)傳輸速率,帶寬的計算公式為:顯存帶寬(GB/s) = 顯存實際頻率(MHz) × 顯存數(shù)據(jù)倍率 × 顯存等效位寬(bit) / 8。GDDR5的頻率可達1750 MHz,采用4倍速率機制,其等效頻率為7000 MHz,但GDDR5內(nèi)部I/O位寬僅32 bit;相比之下,HBM的頻率為500 MHz,采用2倍速率機制,等效頻率為1000 MHz,但HBM內(nèi)部I/O位寬高達1024 bit,將帶寬提升至128 GB/s。HBM之所以能實現(xiàn)32倍于GDDR5的I/O位寬,是因為它采用了堆棧式設計,通過TSV堆棧方式將DRAM裸片垂直堆疊放置,從而實現(xiàn)在相同底面積上布置了數(shù)倍的DRAM顆粒,以達到更高的I/O數(shù)量。2)I/O速率:在數(shù)值上,顯存速率和顯存頻率是相等的,使帶寬計算公式簡化為:顯存帶寬(GB/s) = 顯存數(shù)據(jù)速率(Gbps) × 顯存等效位寬(bit) / 8。這是因為顯存速率表示每秒傳輸?shù)臄?shù)據(jù)位數(shù),單位為bps (bits per second)。顯存頻率以MHz為單位,頻率單位赫茲的本質(zhì)就是,描述了單位時間內(nèi)完成周期性變化的次數(shù)。因此,在數(shù)值上,顯存速率和顯存頻率是相等的。根據(jù)JEDEC固態(tài)技術協(xié)會發(fā)布的HBM3標準,HBM3定義高達6.4 Gb/s的數(shù)據(jù)速率,堆棧中的DRAM芯片數(shù)量(四到十六個)及其具體容量(每堆棧4 GB到64 GB)不等,計算得到初始HBM3堆棧可提供每堆棧819GB/s的傳輸帶寬。

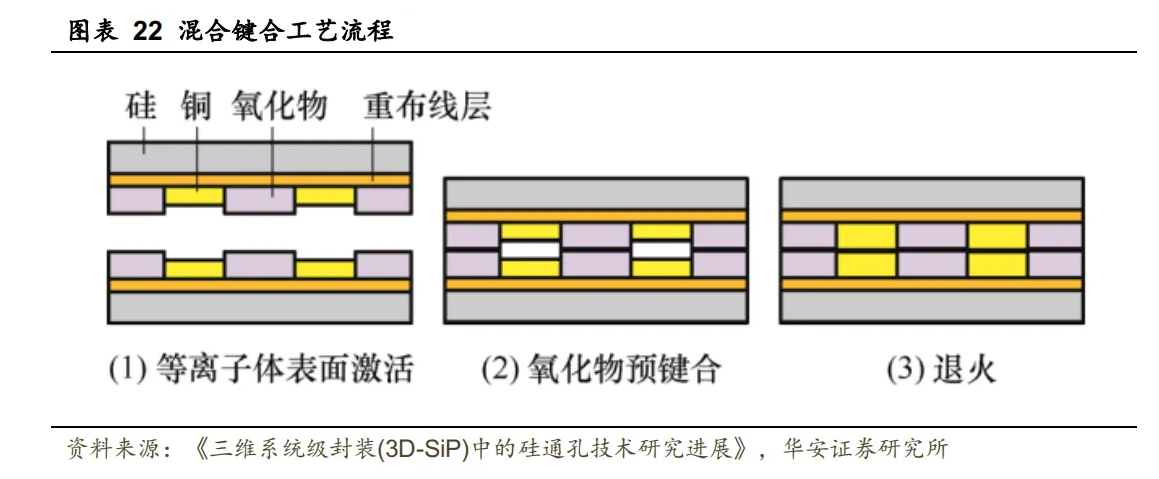

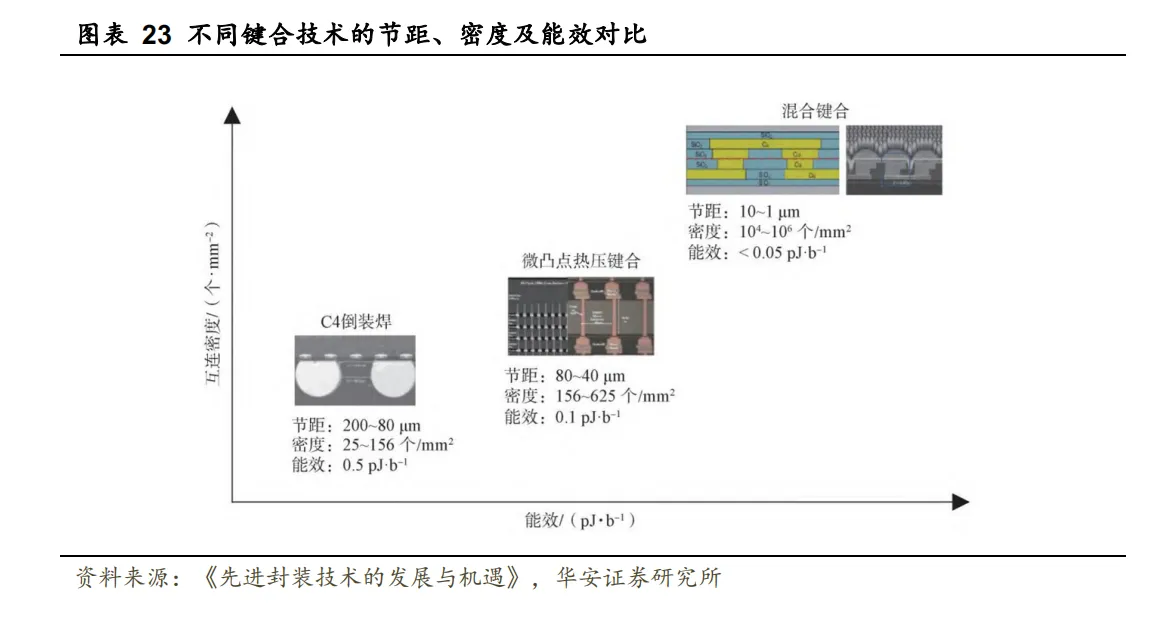

HBM堆棧層數(shù)增加對芯片間鍵合技術提出更高的要求,關鍵改進是使用混合鍵合替代原來的微凸點鍵合。混合鍵合是一種實現(xiàn)介質(zhì)層與介質(zhì)層、金屬與金屬界面無縫隙鍵合的技術,芯片鍵合界面由介質(zhì)層(通常為SiO2)和金屬(通常為Cu)組成。SiO2介質(zhì)層為集成單元提供機械支撐與電氣隔離,Cu-Cu鍵合提供芯片間的垂直電氣互連。對于Cu和SiO2混合鍵合結構,首先要對鍵合表面進行等離子或快速原子束表面激活處理,之后進行直接鍵合,最后進行退火處理。退火在增強SiO2-SiO2鍵合強度的同時,也促進了Cu晶粒的生長和擴散以實現(xiàn)Cu-Cu鍵合。海力士計劃將混合鍵合技術應用于下一代HBM4產(chǎn)品,混合鍵合技術可以大幅縮小電極尺寸,從而實現(xiàn)更高的I/O密度,同時可以顯著縮小芯片之間的間隙,減少產(chǎn)品厚度。

混合鍵合的主要優(yōu)點包括:1)縮小互聯(lián)間距:它可以實現(xiàn)超細間距的芯片互連,比傳統(tǒng)微凸點連接提高了10倍以上。超細間距的連線將增加布線的有效使用面積,增加通道數(shù)量,并實現(xiàn)數(shù)據(jù)處理串并行轉換,簡化I/O端口電路,增大數(shù)據(jù)傳輸帶寬。2)降低信號延時:它可以實現(xiàn)芯片之間的無凸點互連通信,取消微凸點連接,進一步降低通道的寄生電感性和信號延時。3)減薄芯片厚度:混合鍵合可以實現(xiàn)超薄芯片的制備,通過芯片的減薄可以大幅降低芯片的厚度和重量,并進一步提升互連帶寬;4)提高鍵合可靠性:混合鍵合還可以提高鍵合的可靠性,通過分子尺度的銅-銅觸點融合和二氧化硅-二氧化硅的分子共價鍵連接,大幅提高了界面鍵合力,增強了芯片對環(huán)境的適應性。

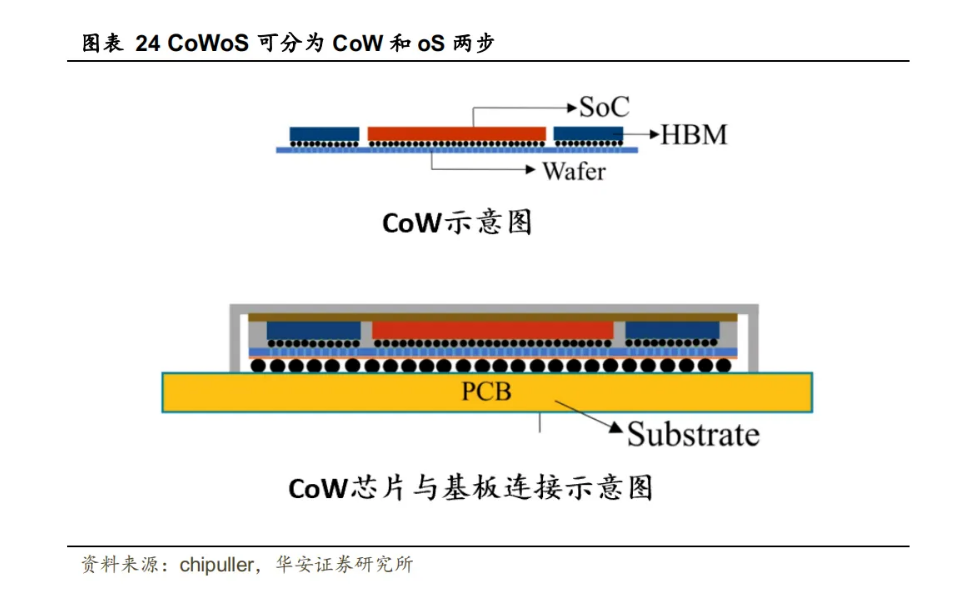

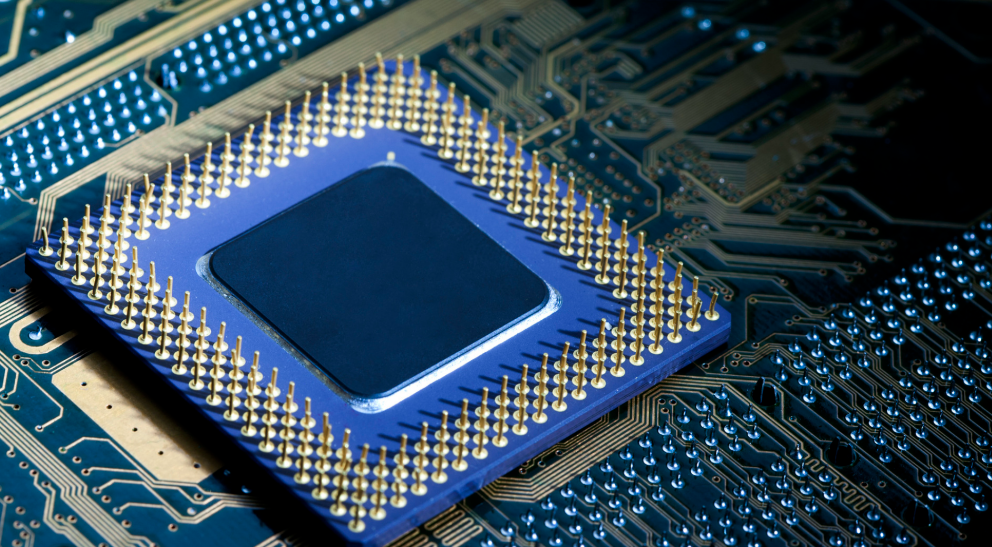

HBM的高密度連接和短互聯(lián)間距,要求臺積電的CoWoS封裝技術。CoWoS是臺積電于2012年研發(fā)的一種2.5D集成封裝技術,可分為CoW和oS兩步,CoW(chip on wafer)是將計算核心、I/O die、HBM等芯片封裝在硅中介層上;然后再把CoW芯片整體封裝在基板(Substrate)上,即oS(on substrate)環(huán)節(jié)。CoWoS可以節(jié)省空間,實現(xiàn)HBM所需的高互聯(lián)密度和短距離連接;還能將不同制程的芯片封裝在一起,在滿足AI、GPU等加速運算的需求的同時控制成本。目前所有先進的AI計算芯片都使用HBM,而幾乎所有HBM都封裝在CoWoS上。

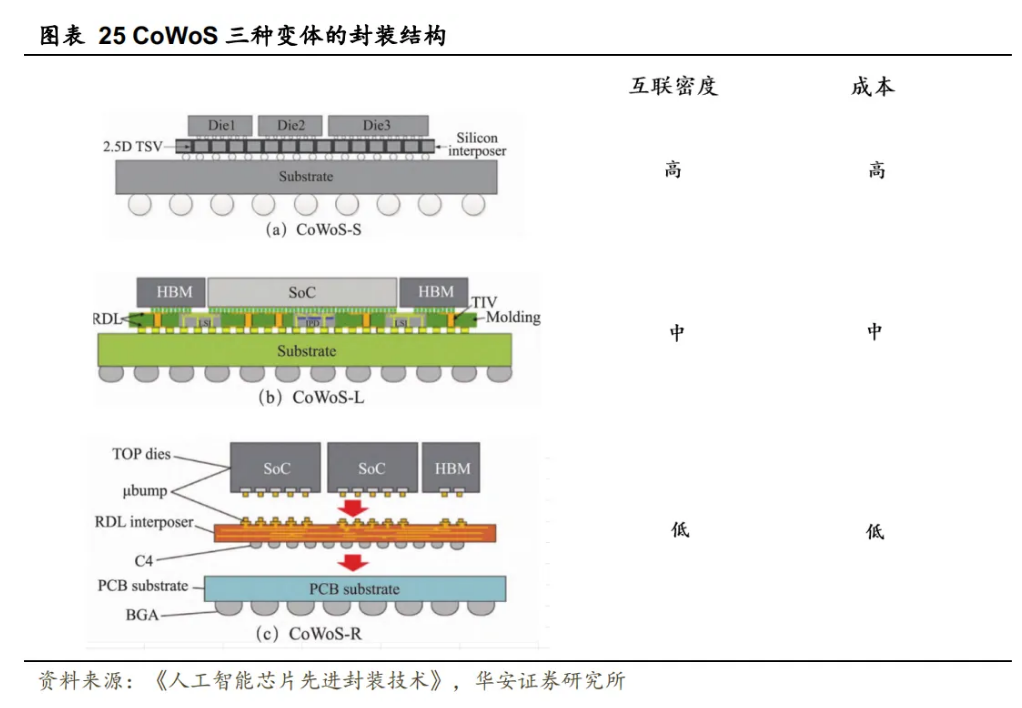

根據(jù)中介層材料的不同,CoWoS有三種變體:CoWoS-S(中介層是Si襯底)、CoWoS-R(中介層由RDL構成)和CoWoS-L(中介層由Chiplet和RDL組成),其中CoWoS-S為量產(chǎn)主要配置。CoWoS-S利用硅片作為橋梁,芯片互聯(lián)密度最高;出于成本的考慮,CoWoS-R采用有機轉接板,但也導致芯片互聯(lián)密度較低;CoWoS-L將小硅橋安裝在有機轉接板中,僅在芯片鏈接部分使用硅片,實現(xiàn)鄰近芯片邊緣的高密度連接,生產(chǎn)成本和性能介于CoWoS-R和CoWoS-S之間。

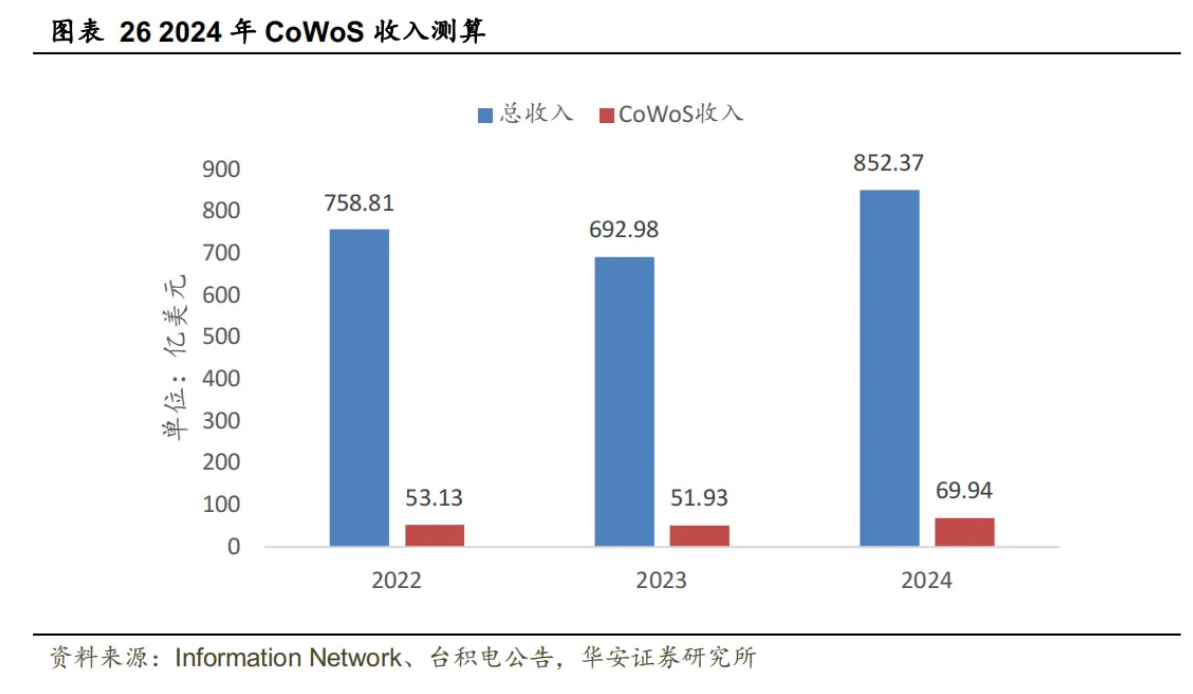

2024年,CoWoS預計為臺積電帶來70億美元營收。AI需求驅動下,CoWoS在臺積電營收的比重逐漸上升。根據(jù)Information Network估計,2022/2023/2024年CoWoS收入占臺積電營收的比例將分別達到7.00%/7.49%/8.21%。以臺積電2024年全年營收指引852.37億美元估算,AI將帶來約69.94億美元的CoWoS營收,較2023年同比增長34.69%。

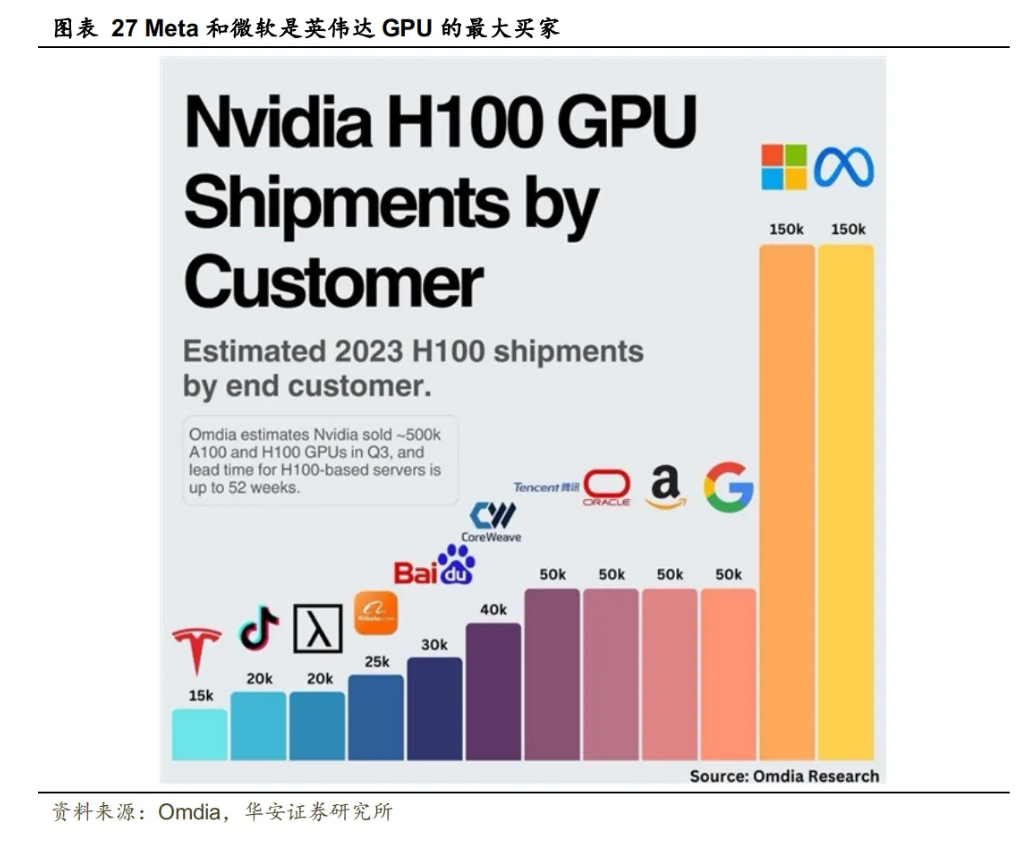

CoWoS的絕大多數(shù)需求來自AI。英偉達的H100、A100均由臺積電代工,并使用CoWoS先進封裝。根據(jù)Omdia,2023Q3英偉達售出近50萬個A100和H100 GPU,Meta和微軟是最大買家,其次是谷歌、亞馬遜、甲骨文和騰訊。得益于人工智能和高性能計算的需求,本財年第三季度,Nvidia在數(shù)據(jù)中心硬件上獲得了145億美元的收入。龐大的需求量導致CoWoS產(chǎn)能供不應求。除了英偉達外,AMD的最新AI GPU產(chǎn)品MI300也導入臺積電的CoWoS(2.5D)和SoIC(3D)的技術。此外,還有一系列ASIC芯片,如英特爾的Habana Gaudi、谷歌的TPU v5e、亞馬遜的Inferentia和Trainium芯片等。

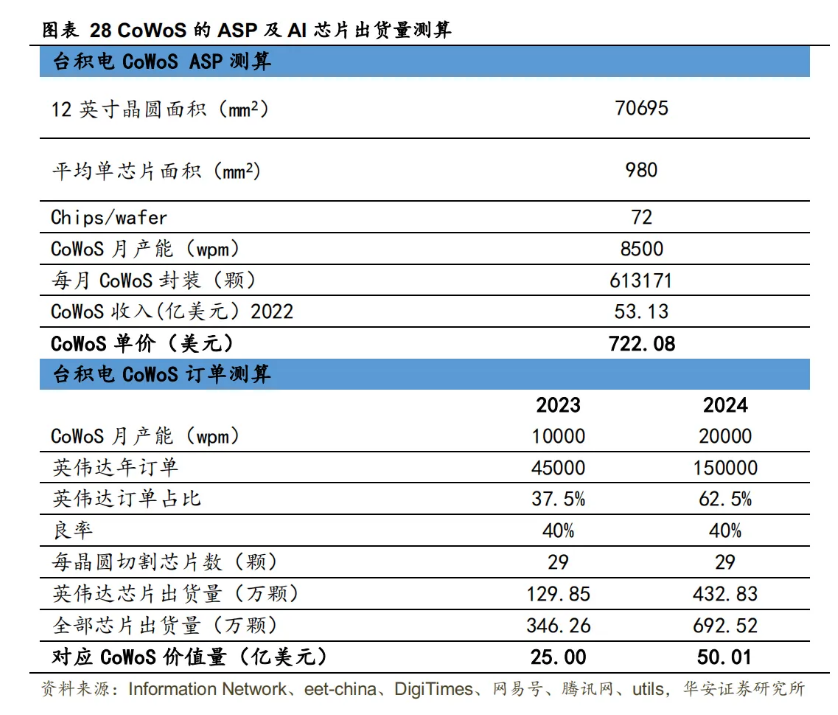

根據(jù)我們的測算,CoWoS封裝的單價為722.08美元/顆,2023年/2024年基于CoWoS的芯片出貨量將達到346萬顆/693萬顆,其中供給英偉達的芯片分別為130萬顆/433萬顆。按照12英寸晶圓面積70695 mm2和H100、A100、Epic Genoa、MI300四種AI芯片平均面積980mm2,測算得到每張晶圓上芯片數(shù)約72顆。根據(jù)Information Network給出的2022年CoWoS月產(chǎn)能為8500片以及前文測算的2022年臺積電CoWoS收入,得到單顆芯片CoWoS封裝價格約為722.08美元。而根據(jù)DigiTimes的報道,2023年CoWoS年產(chǎn)能約12萬片,2024年將沖上24萬片,其中英偉達將取得14.4-15萬片。由于這些芯片多在7nm和5nm節(jié)點生產(chǎn),保守假設良率為40%。我們以英偉達2023年和2024年分別取得4.5萬片和15萬片的產(chǎn)能來算,預計英偉達出貨量約130萬顆和433萬顆。全體AI芯片出貨量約346萬顆和693萬顆,對應2023年/2024年CoWoS將產(chǎn)生25億美元/50億美元收入。

供需短缺情況將在13個月內(nèi)得到緩解,非臺積供應鏈(non TSMC)有機會受益。臺積電已于2023年第二季度開始采取行動擴產(chǎn),包括將部分InFO產(chǎn)能從龍?zhí)掇D移至南科,以便在龍?zhí)掇D擴CoWoS產(chǎn)能。2023年7月25日,臺積電宣布擬投資900億新臺幣(約206億元人民幣)于竹科轄下銅鑼科學園區(qū)新建先進封裝廠,以加速擴產(chǎn)CoWoS產(chǎn)能,預計2026年底建廠完成,2027年開始量產(chǎn)。此外,臺積電同時也將部分委外至其他封測廠,聯(lián)電、安靠、矽品等均提供產(chǎn)能支持。影響CoWoS擴產(chǎn)的關鍵是設備交貨時間較長。臺積電董事長劉德音在2023年9月6日出席大師論壇專題演講會時稱,CoWoS預期1年半后可100%滿足客戶需求。因此對非臺積供應鏈來說,在CoW端接單的窗口期已不足13個月,加之擴產(chǎn)時間考慮,各封測廠商對于擴產(chǎn)態(tài)度與規(guī)模較為保守。

芯片封裝清洗劑選擇:

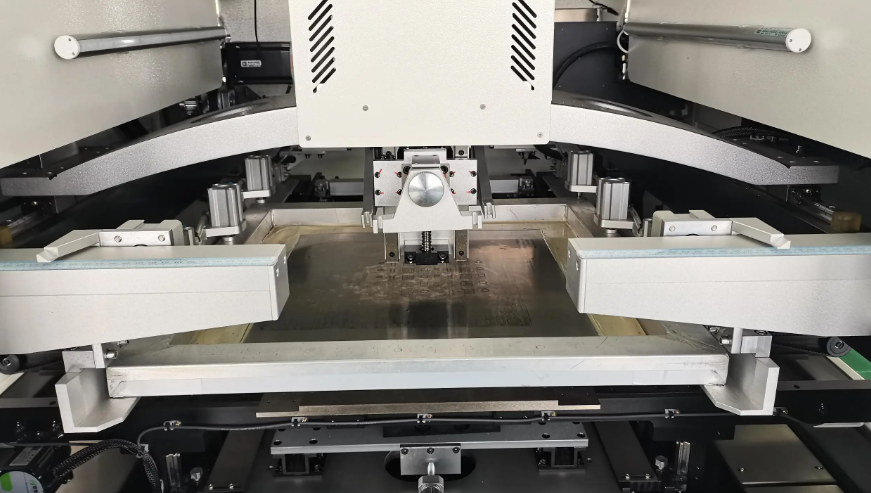

水基清洗的工藝和設備配置選擇對清洗精密器件尤其重要,一旦選定,就會作為一個長期的使用和運行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環(huán)境中的濕氣,通電后發(fā)生電化學遷移,形成樹枝狀結構體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內(nèi)的浮點、灰塵、塵埃等,這些污染物會導致焊點質(zhì)量降低、焊接時焊點拉尖、產(chǎn)生氣孔、短路等等多種不良現(xiàn)象。

這么多污染物,到底哪些才是最備受關注的呢?助焊劑或錫膏普遍應用于回流焊和波峰焊工藝中,它們主要由溶劑、潤濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質(zhì)在所有污染物中的占據(jù)主導,從產(chǎn)品失效情況來而言,焊后殘余物是影響產(chǎn)品質(zhì)量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質(zhì)引發(fā)接觸電阻增大,嚴重者導致開路失效,因此焊后必須進行嚴格的清洗,才能保障電路板的質(zhì)量。

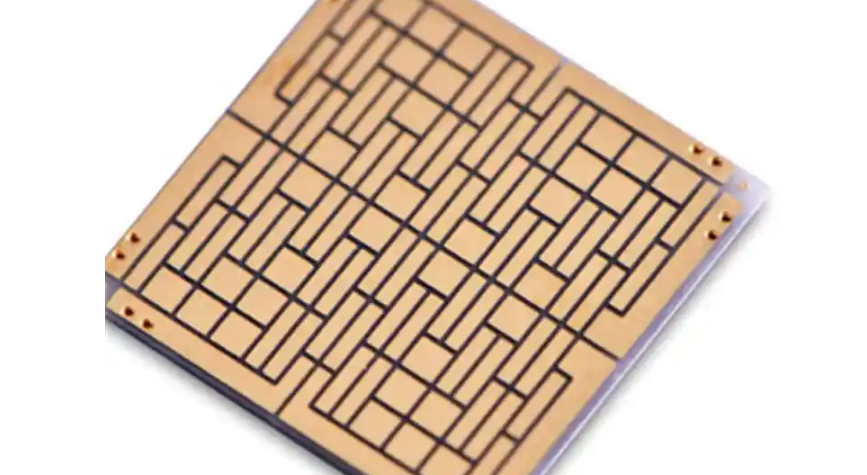

合明科技研發(fā)的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

合明科技運用自身原創(chuàng)的產(chǎn)品技術,滿足芯片封裝工藝制程清洗的高難度技術要求,打破國外廠商在行業(yè)中的壟斷地位,為芯片封裝材料全面國產(chǎn)自主提供強有力的支持。

推薦使用合明科技水基清洗劑產(chǎn)品。

![[x]](/template/default/picture/closeimgfz1.svg)