因?yàn)閷I(yè)

所以領(lǐng)先

由于圖案微型化技術(shù)的發(fā)展,這一預(yù)測被稱為摩爾定律,直到最近才得以實(shí)現(xiàn)。然而,摩爾定律可能不再有效,因?yàn)榧夹g(shù)進(jìn)步已達(dá)到極限,并且由于使用極紫外 (EUV) 光刻系統(tǒng)等昂貴設(shè)備而導(dǎo)致成本上升。與此同時(shí),市場對不斷完善的半導(dǎo)體技術(shù)的需求仍然很大。為了彌補(bǔ)技術(shù)進(jìn)步方面的差距并滿足半導(dǎo)體市場的需求,出現(xiàn)了一種解決方案: 先進(jìn)的半導(dǎo)體封裝技術(shù)。

盡管先進(jìn)封裝非常復(fù)雜并且涉及多種技術(shù),但互連技術(shù)仍然是其核心。

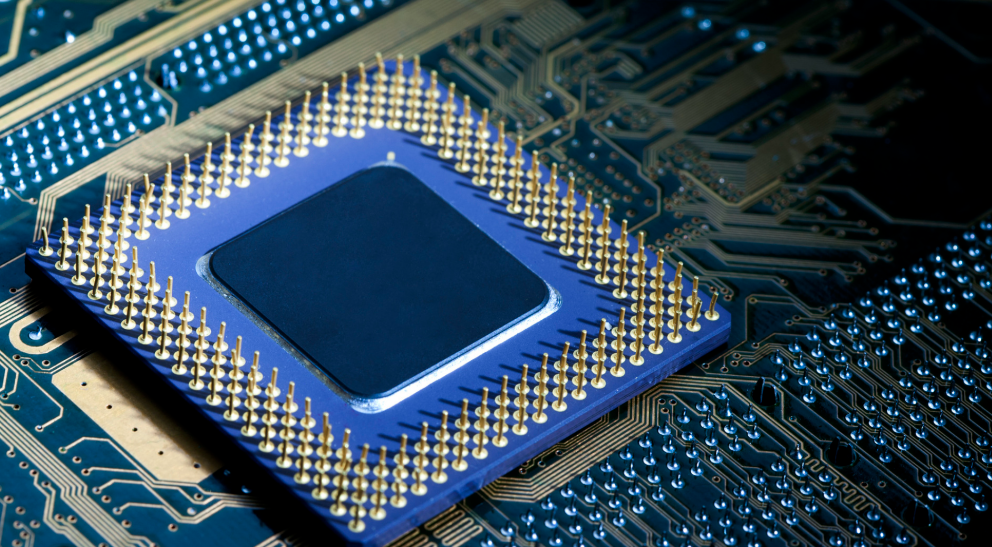

首先,需要注意的是,互連技術(shù)是封裝中關(guān)鍵且必要的部分。芯片通過封裝互連以接收電力、交換信號并最終進(jìn)行操作。由于半導(dǎo)體產(chǎn)品的速度、密度和功能根據(jù)互連方式而變化,因此互連方法也在不斷變化和發(fā)展。

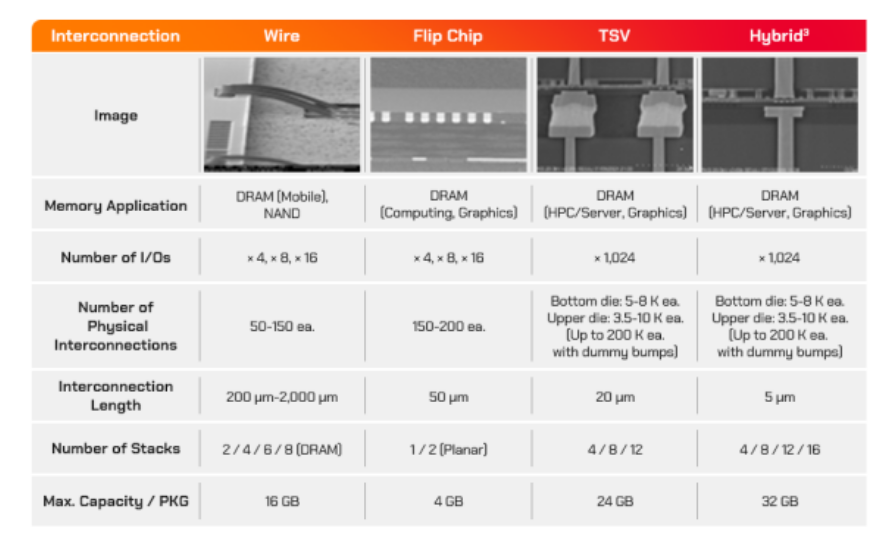

除了開發(fā)各種工藝以在晶圓廠實(shí)現(xiàn)精細(xì)圖案外,還全面努力推進(jìn)封裝工藝中的互連技術(shù)。因此,開發(fā)了以下四種類型的互連技術(shù):引線鍵合、倒裝芯片鍵合、硅通孔 (TSV) 鍵合以及小芯片混合鍵合。

1硅通孔 (TSV):一種垂直互連通路(通孔),完全穿過硅芯片或晶圓,以實(shí)現(xiàn)硅芯片的堆疊。

2 Chiplet:按用途(例如控制器或高速存儲器)劃分芯片并將其制造為單獨(dú)的晶圓,然后在封裝過程中重新連接的技術(shù)。

3下述產(chǎn)品未采用混合鍵合。規(guī)格為估計(jì)值。

圖 1. 互連方法規(guī)格表。(這些規(guī)格是應(yīng)用每種互連技術(shù)的主要產(chǎn)品的示例。)

1.引線鍵合

引線鍵合是第一種開發(fā)的互連方法。通常,具有良好電性能的材料(例如金、銀和銅)被用作連接芯片和基板的導(dǎo)線。這是最具成本效益且可靠的互連方法,但由于其電氣路徑較長,因此不適合需要高速操作的較新設(shè)備。因此,這種方法被用于不需要快速操作的移動設(shè)備中使用的移動 DRAM 和 NAND 芯片。

2.倒裝芯片接合

倒裝芯片接合 克服了引線鍵合的缺點(diǎn)。其電氣路徑的長度是引線鍵合的十分之幾,使其適合高速操作。與在芯片級執(zhí)行的引線鍵合相比,在晶圓級進(jìn)行處理的倒裝芯片鍵合還提供了卓越的生產(chǎn)率。因此,它被廣泛應(yīng)用于CPU、GPU和高速DRAM芯片的封裝。此外,由于可以在芯片的整個(gè)側(cè)面形成凸塊,因此可以比引線鍵合擁有更多的輸入和輸出 (I/O),從而有可能提供更高的數(shù)據(jù)處理速度。然而,倒裝芯片接合也有其自身的缺點(diǎn)。首先,難以進(jìn)行多芯片堆疊,這對于需要高密度的存儲產(chǎn)品來說是不利的。此外,盡管倒裝芯片鍵合可以比引線鍵合連接更多的 I/O,和有機(jī) PCB 間距阻止連接更多數(shù)量的 I/O。為了克服這些限制,開發(fā)了 TSV 鍵合技術(shù)。

3.硅通孔 (TSV) 鍵合

TSV不采用傳統(tǒng)的布線方法來連接芯片與芯片,而是通過在芯片上鉆孔并填充金屬等導(dǎo)電材料以容納電極來垂直連接芯片。制作帶有TSV的晶圓后,通過封裝在其頂部和底部形成微凸塊,然后連接這些凸塊。由于 TSV 允許凸塊垂直連接,因此可以實(shí)現(xiàn)多芯片堆疊。最初,使用 TSV 接合的堆棧有四層,后來增加到八層。最近,一項(xiàng)技術(shù)使得堆疊 12 層成為可能,并于 2023 年 4 月SK hynix 開發(fā)了其 12 層 HBM3。雖然 TSV 倒裝芯片接合方法通常使用基于熱壓的非導(dǎo)電薄膜 (TC-NCF),但 SK hynix 使用 MR-MUF 4 工藝,可以減少堆疊壓力并實(shí)現(xiàn)自對準(zhǔn)。5這些特性使 SK hynix 能夠開發(fā)出世界上第一個(gè) 12 層 HBM3。

4大規(guī)模回流模塑底部填充(MR-MUF):將半導(dǎo)體芯片堆疊起來,并將液體保護(hù)材料注入芯片之間的空間,然后硬化以保護(hù)芯片和周圍電路的工藝。與在每個(gè)芯片堆疊后應(yīng)用薄膜型材料相比,MR-MUF 是一種更高效的工藝,并提供有效的散熱。

5自對準(zhǔn):在 MR-MUF 工藝期間通過大規(guī)模回流將芯片重新定位到正確的位置。在此過程中,熱量被施加到芯片上,導(dǎo)致相關(guān)凸塊在正確的位置熔化并硬化。

與小芯片的混合鍵合

術(shù)語“混合”用于表示同時(shí)形成兩種類型的界面結(jié)合6 。界面結(jié)合的兩種類型是:氧化物界面之間的結(jié)合和銅之間的結(jié)合。這項(xiàng)技術(shù)并不是新開發(fā)的技術(shù),但多年來已經(jīng)用于 CMOS 圖像傳感器的大規(guī)模生產(chǎn)。然而,由于小芯片的使用增加,它最近引起了更多關(guān)注。Chiplet技術(shù)將各個(gè)芯片按功能分離,然后通過封裝將它們重新連接起來,在單個(gè)芯片上實(shí)現(xiàn)多種功能。

6界面鍵合:相互接觸的兩個(gè)物體的表面通過分子間力結(jié)合在一起的鍵合。

盡管小芯片的功能是該技術(shù)的一個(gè)明顯優(yōu)勢,但采用它們的主要原因是成本效益。當(dāng)所有功能都在單個(gè)芯片上實(shí)現(xiàn)時(shí),芯片尺寸會增加,并且不可避免地導(dǎo)致晶圓生產(chǎn)過程中良率的損失。此外,雖然芯片的某些區(qū)域可能需要昂貴且復(fù)雜的技術(shù),但其他區(qū)域可以使用更便宜的傳統(tǒng) 技術(shù)來完成。因此,由于芯片無法分離,制造工藝變得昂貴,因此即使只有很小的面積需要精細(xì)技術(shù),也要將精細(xì)技術(shù)應(yīng)用于整個(gè)芯片。然而,小芯片技術(shù)能夠分離芯片功能,從而可以使用先進(jìn)或傳統(tǒng)的制造技術(shù),從而節(jié)省成本。

雖然chiplet技術(shù)的概念已經(jīng)存在十多年了,但由于缺乏能夠互連芯片的封裝技術(shù)的發(fā)展,它并沒有被廣泛采用。然而,芯片到晶圓 (C2W) 混合鍵合的最新進(jìn)展顯著加速了小芯片技術(shù)的采用。C2W 混合鍵合具有多種優(yōu)勢。首先,它允許無焊料鍵合,從而減少鍵合層的厚度、縮短電氣路徑并降低電阻。因此,小芯片可以高速運(yùn)行而無需任何妥協(xié)——就像單個(gè)芯片一樣。其次,通過直接將銅與銅接合,可以顯著減小凸塊上的間距。目前,使用焊料時(shí)很難實(shí)現(xiàn) 10 微米 (μm) 或更小的凸塊間距。然而,銅對銅直接鍵合可以將間距減小到小于一微米,從而提高芯片設(shè)計(jì)的靈活性。第三,它提供了先進(jìn)的散熱功能,這一封裝功能在未來只會繼續(xù)變得越來越重要。最后,上述的薄粘合層和細(xì)間距影響了封裝的形狀因數(shù),因此可以大大減小封裝的尺寸。

![[x]](/template/default/picture/closeimgfz1.svg)