因為專業

所以領先

8月8日至11日,第二十四屆電子封裝技術國際會議(CEPT 2023)在新疆進行。ICEPT2023大會報告直面電子封裝當下的難題和挑戰,從系統集成與平臺、新材料、新工藝以及新設備給出指導性出路。

本次大會由中國科學院微電子研究所、石河子大學、國際電氣電子工程師協會電子封裝學會(IEEE-EPS)和中國電子學會電子制造與封裝技術分會(CIE-EMPT)主辦,在石河子大學召開,由 IEEE 電子封裝學會(EPS)提供技術支持。

會議吸引來自海內外學術界和工商界超700名專家學者、研究人員、企業人士會師西域新疆、齊聚一堂、共享碩果,推動先進封裝面向技術創新、學術交流與國際合作!

開幕致辭中各位領導與嘉賓對ICEPT2023勝利召開表示慶賀!大會報告嘉賓來自IEEE EPS、石河子黨政機關,以及石河子大學、長電科技、東京大學/日本明星大學、北方華創、海光信息、加州大學、ULVAC、EVG、拉瑪爾大學、中國科學院微電子研究所等知名企業、研究院所與高校的專家教授。

ICEPT 2023踐行產學研深度融合的時代使命

后摩爾時代背景下,半導體制造技術面臨挑戰,新技術不斷涌現,先進封裝在產業鏈中的地位愈加重要。新研發、新技術、新材料以及新的產學研交互方式,成為電子封裝技術尤其是先進封裝產業發展,極其重要的進步環節。作為國際上最著名的電子封裝技術會議之一,ICEPT會議得到了IEEE-EPS的全力支持和中國電子學會、中國科協的高度評價,已成為國際電子封裝領域四大品牌會議之一。

ICEPT2023首次在大美新疆舉辦,寄托了各方的美好愿望,踐行了ICEPT產學研深度融合、促進電子封裝技術國際合作的時代使命。ICEPT2023為與會專家學者深入了解新疆,認識新疆提供了一次良好的機遇,為電子工裝產業鏈融合提供一個典型的視角,大家以此次會議為契機,深入研討,促進合作,共同為電子封裝產學研融合的發展貢獻智慧和力量。

推動先進封裝面向技術創新,大會報告精彩紛呈

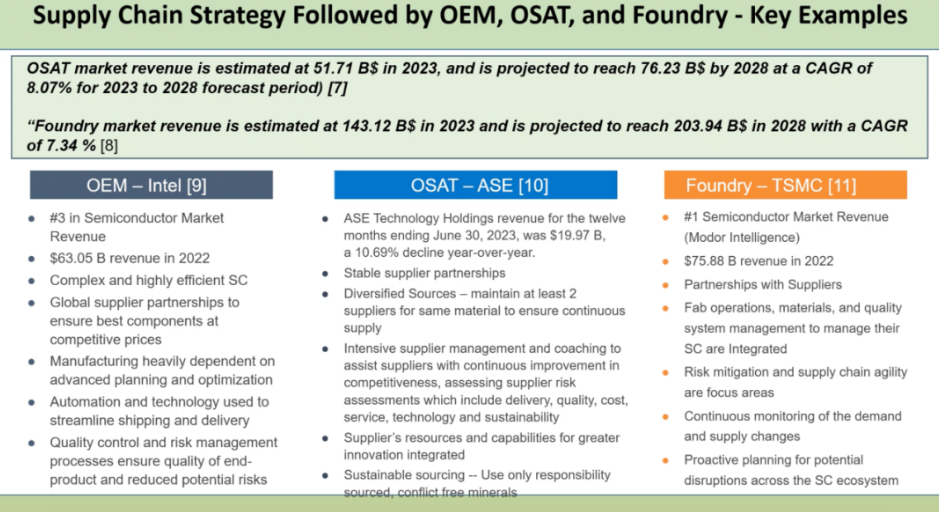

報告1:異構集成供應鏈半導體封裝的供應鏈趨勢、挑戰和變革

美國IEEE EPS主席 Kitty PEARSALL博士在演講中簡要回顧了多年來供應鏈轉型,直至當今的全球電子封裝格局并通過物聯網進行整合。該行業已經從全球一體化公司轉向 OEM/IDM、OSAT 和代工廠。這種轉變導致全球半導體封裝供應鏈面臨更多不確定性。流行病、地緣政治和區域戰略挑戰對電子供應鏈造成的干擾。工廠在數字化和優化其主要制造流程、利用人工智能/MI以及處理大量數據方面面臨著挑戰。她還談到了半導體封裝的驅動因素以及供應鏈中斷問題。

OEM、OSAT和代工所遵循的供應鏈策略-關鍵示例

報告2:高性能封裝創新推動微系統集成變革

長電科技CEO鄭力先生在演講中提到高性能封裝承載了芯片成品制造技術的持續創新方向,將重塑集成電路產業發展模式。高性能封裝創新解決供電系統集成難題,高性能2.5D/3D封裝創新推動高性能計算、多芯片微系統異質異構集成;高性能先進封裝的主要特征(如芯片-封裝功能融合)。新一代微系統集成設計方法論的革新如(STCO)……

長電科技CEO 鄭力 先生

結論總結中指出,微系統集成推動集成電路創新,延續摩爾定律;高性能先進封裝是微系統集成的關鍵路徑;高性能先進封裝需要業界和學術界更廣范圍的技術合作;高性能先進封裝對新材料,新工藝設備的革命性需求日益強烈。

在高性能封裝領域,長電科技近年來投入了大量資源,并面向高性能計算等領域推出了Chiplet高性能封裝技術平臺XDFOI?,目前已實現穩定量產。

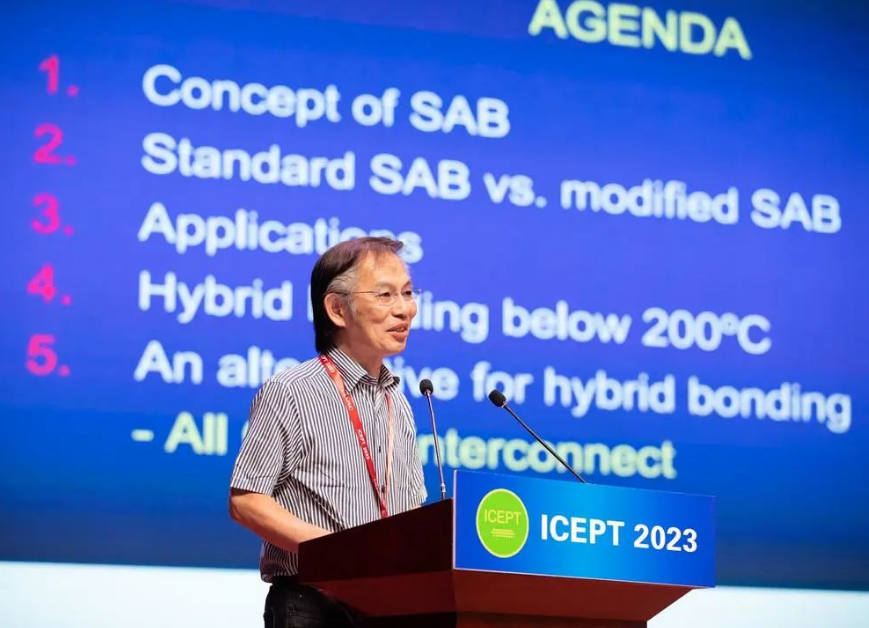

報告3:適用于低溫三維集成的表面活化鍵合

日本東京大學名譽教授,日本明星大學教授Tadatomo SUGA 在演講中提到低溫粘合的先進方法有從表面活化及其未來展望3D集成的發展。

日本東京大學名譽教授,日本明星大學教授 Tadatomo SUGA

目前技術用于互連和接合包括氧化物接合、陽極接合、玻璃料接合,焊接、共晶結合、金屬擴散結合,超聲波粘接、粘接等,在這些粘合過程中需要高溫傳統方法的主要瓶頸。由于設備可靠性和制造產量,尤其是在異質性由不同材料組成的一體化。表面活性鍵合(SAB)方法已經吸引了越來越多的人興趣由于其簡單的流程,不需要用于粘合的附加材料,以及與CMOS技術。

回顧了表面活化低溫鍵合的先進方法及其 3D 集成的發展。介紹了一種新的室溫鍵合方法,可以將硅氧化物、玻璃和藍寶石等無機材料相互鍵合,也可以與聚合物薄膜鍵合。該方法基于表面活化鍵合(SAB),并進行了一些修改,包括形成鐵納米粘合層以及由特殊離子束源形成的附加硅中間層。人們發現,這種材料的晶片可以在室溫下非常牢固地粘合,無需任何熱處理。該方法還可以應用于無需任何有機粘合劑的聚合物與聚合物的粘合。

報告4:先進封裝中的金屬薄膜設備及工藝挑戰

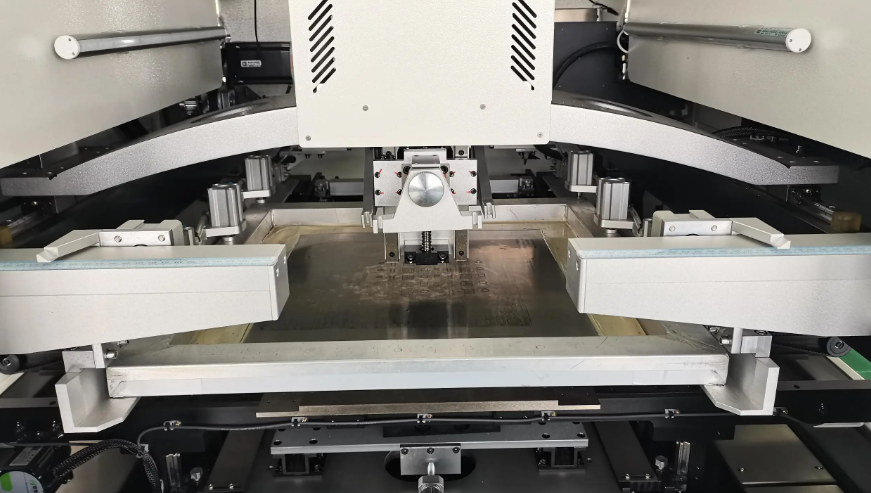

北方華創PVD事業單元副總經理耿波先生分享了金屬薄膜設備整體解決方案。

北方華創是半導體設備龍頭,國產替代空間廣闊。近年來在先進封裝高速帶動下,公司聚焦半導體后道封裝設備領域,面對先進封裝中的金屬薄膜設備及工藝挑戰,推出了TSV和銅曝光工藝整體解決方案,為國內封裝廠推出了本土化的先進設備解決方案。

如今北方華創不斷加快科研步伐,通過持續的技術迭代與創新,以不斷精進的產品與服務推動中國先進封裝邁向新的時代。

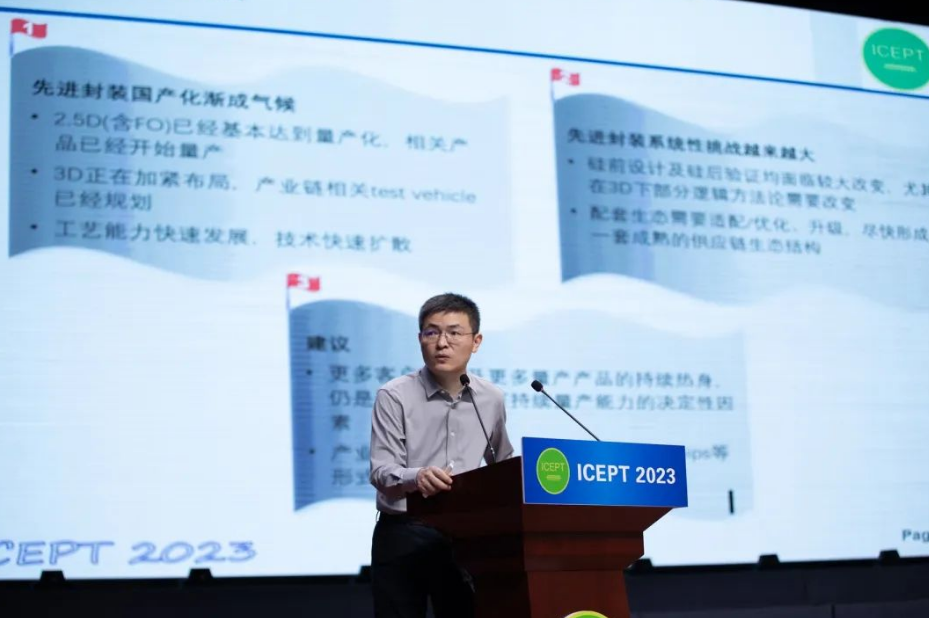

報告5:先進封裝國產化發展趨勢及產品化挑戰

海光信息總裁助理、主任工程師李成先生在演講中表述,基于 2.5D 及 3D 從工程到量產的快速發展,國內相關技術迭代加快,在此過程中國內工藝廠利用后發的資金、人才優勢可以加快技術發展;產品公司則從市場化角度共同推動產品化的更優技術路線,可以實現后發成本、技術優勢。

海光信息總裁助理、主任工程師 李成 先生

他還重點針對 2.5D 的不同技術路線的產品化驗證并進行比較。同時未來在先進封裝尤其是 3D 封裝下,除了工藝挑戰外,對產品公司也提出了更高挑戰,包括產品設計、產品定義、硅后封測邏輯等,形成系統化的解決方案才能最大化利用好先進封裝的優勢。

報告6:整體靜電保護協同設計

美國加州大學王自慧教授表示靜電放電(ESD)保護一直是集成電路(IC)和微電子系統(包括裸芯片和封裝微芯片)中一個主要的可靠性問題。

任何片上/封裝內/板上的靜電放電保護都不可避免地會影響系統性能。另一方面,三維異構集成(HI)技術和異構集成微系統給靜電放電保護設計帶來新的復雜性。因此,整體的靜電放電保護協同設計對先進的微系統芯片至關重要。演講中著重介紹新興的靜電放電保護設計挑戰,并討論未來芯片靜電放電保護的一些展望。

報告7:面向內存計算的異構集成制造技術

來自日本愛發科株式會社總裁兼CEO Koukou Suu 博士分享了面向內存計算的異構集成制造技術。

愛發科株式會社總裁兼CEO Koukou Suu 博士

5G/6G時代的智能通信技術將由“云AI計算”和“霧/邊緣AI計算”構建,從而實現精確匹配和低延遲(<1ms)通信。物聯網/物聯網智能系統是通過獨立的自激活微機電系統/傳感器等智能功能實現的。這些將在未來帶來一個全面的“智能社會”。另一方面,盡管摩爾定律正在放緩,但對人工智能性能的要求正在迅速提高。異構集成作為一種先進的封裝技術,是實現高性能人工智能芯片的解決方案之一。

“近內存”和“內存計算”是模擬人工智能的關鍵技術。這些新架構和新計算不僅是異構集成的必要條件,也是非易失性內存的必要條件。ULVAC一直在不斷開發非易失性存儲器(PCRAM、ReRAM、FeRAM)和異構集成(2.nD、3D、FO-WLP/PLP、高密度有機中介層和TSV)的制造技術。

報告8:用于下一代先進互連技術的混合鍵合

來自奧地利EVG公司BD經理 Anton Alexeev 博士介紹了用于下一代先進互連技術的混合鍵合技術。

奧地利EVG公司BD經理 Anton Alexeev 博士

晶圓對晶圓混合鍵合在過去十年獲得極大關注,因為它在晶圓級互連制造方面具有主要優勢。裸片到晶圓的工藝流程作為一種替代工藝得到開發。這種方法是建立在已知合格芯片原則基礎上的:在晶圓制造之后,裸片將進行切割,通過質量標準的裸片被用于在晶圓上鍵合。這樣,由于單個晶圓的良率損失而導致的鍵合良率損失將降到最低。

演講中對兩種類型的混合鍵合進行概述,將介紹兩種類型的裸片到晶圓的工藝流程,將回顧該技術的主要規格和一些主要挑戰對工藝結果的影響,將強調采用新計量和調查方法的重要性。

報告9:CPO的今生、前世及未來

張源女士是板級和封裝工程領域的資深講師。演講中概要介紹對CPO/NPO/LPO的理解,分析其價值及潛在應用場景。

張源 女士 專家級講師

她闡述了行業主流企業CPO的研究歷程及趨勢,剖解其中的關鍵技術。分析說明光電合封的產業鏈挑戰,以及標準狀況。

隨著數據需求量的不斷增加,需要處理器、交換等核心芯片的性能不斷提升,而半導體納米工藝的步伐漸緩,使得封裝功耗、物理尺寸、IO速率不斷挑戰工程極限。相對電互連,光互連本身具備大帶寬、長距傳輸等優勢,而硅光的產業化,更加推動了“光進銅退”的演進,使得光互連進封裝(CPO)、進單板(NPO)成為了行業熱點。

報告10:從電遷移到熱遷移:封裝設計規則的根本改變

美國拉瑪爾大學教授樊學軍博士介紹了本課題的重要內容。隨著高性能半導體的需求不斷增加,采用 3D 單片和 2.5D/3D 先進封裝技術的異構集成能夠顯著提高系統性能。因此,電遷移(EM)誘發的微凸塊和再分布線(RDL)失效已經成為人們關注的焦點。

美國拉瑪爾大學教授 樊學軍 博士

此外,焦耳加熱誘發的熱遷移(TM)與電遷移相結合,正在成為微/納米電子未來的一大潛在風險。在這次演講中,我將在全耦合建模的基礎上,介紹由電遷移(EM)所致失效的設計規則和加速測試的一些一般準則。多年來,現有的 EM 理論只能部分預測或解釋實驗中的復雜現象。最近,我們在耦合理論的框架下梳理出許多不正確的模型和假設。

考慮到多尺度效應,我們用分子動力學模擬確定了關鍵的微觀參數,進而建立了一個完整、自洽的電遷移多物理場耦合模型。為驗證模型,我們進一步進行了全面的 EM 測試,并收集了一致的測試數據。理論和數值結果完全再現了實驗中的各種現象,包括熱遷移的影響。隨后,我們采用經過驗證的理論為設計規則和加速因子提供了新視角,以防止 EM 誘發的失效。

報告11:面向芯粒集成的先進封裝技術

中國科學院微電子研究所封裝中心主任王啟東博士結合目前集成電路行業發展趨勢與Chiplet芯粒集成技術的需求,深入探討了先進封裝技術目前的發展狀態、關鍵技術難點與下一階段的發展路線,并對Chiplet技術在中國的發展做進一步展望。Chiplet芯粒集成技術包括先進封裝技術(MCM、Interposer、TSV等),元器件與接口技術(IP、功能、接口、協議等)和新生態(可信芯片、新EDA、新開發方式等)以及配套的供電與散熱系統等幾個方面。

通過芯粒集成技術,Chiplet 能實現“系統集成,增加功能密度,降低成本”的效果,解決了芯片存儲墻、面積墻、功率墻、功能墻等一系列問題,加之傳遞電路與器件的創新技術,可進一步提高電子產品價值,促進產業效益與規模提升。目前芯粒技術的支撐領域也非常廣闊,包括新一代移動通信、高性能計算、自動駕駛以及物聯網等。

伴隨著第24屆電子封裝技術國際會議(ICEPT2023)大會報告的結束,ICEPT 2023圓滿落幕。隨著一批重大戰略性基礎設施工程的加速推進,我們希望能夠在新一輪的高質量發展進程中,打破美西方的壟斷,不斷地實現材料、封裝技術各個方面的突破,以至于我們能夠為國家的電子信息技術的發展,能夠做出我們新疆、做出我們八師、兵團的貢獻。ICEPT專家學者企業家以此次會議為契機,緊盯“卡脖子”技術,深入地交流研討,形成一批有分量的成果,為建設科技強國貢獻力量。

信息來源:未來半導體

![[x]](/template/default/picture/closeimgfz1.svg)