因為專業

所以領先

Chiplet技術

簡單來說,Chiplet技術就是像搭積木一樣,把一些預先生產好的實現特定功能的裸芯片(Chip)通過先進封裝技術集成在一起形成一個系統級芯片,而這些基本的裸芯片就稱為Chiplet。

Chiplet芯片可以使用更可靠和更便宜的技術制造,較小的硅片本身也不太容易產生制造缺陷。此外,Chiplet芯片也不需要采用同樣的工藝,不同工藝生產制造的Chiplet可以通過SiP技術有機地結合在一起。

Chiplet技術的出現帶來了芯片設計的新趨勢,我們簡單描述為:IP芯片化、集成異構化、IO增量化,簡稱三大技術趨勢。

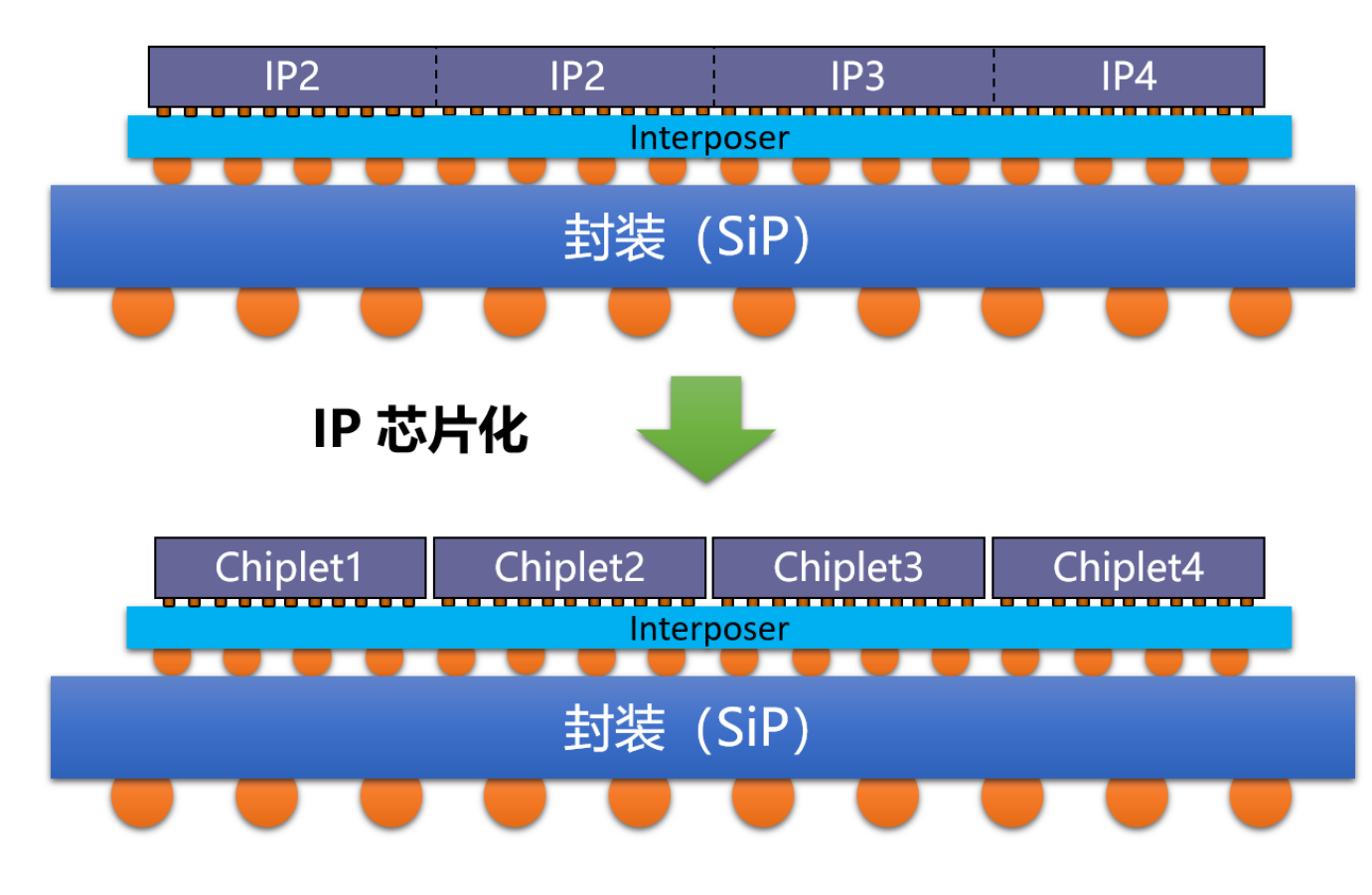

一. IP芯片化

IP(Intellectual Property)是具有知識產權內核的集成電路的總稱,是經過反復驗證過的、具有特定功能的宏模塊,可以移植到不同的半導體工藝中。

到了SoC階段,IP核設計已成為ASIC電路設計公司和FPGA提供商的重要任務,也是其實力的體現。對于芯片開發軟件,其提供的IP核越豐富,用戶的設計就越方便,其市場占用率就越高。目前,IP核已經變成SoC系統設計的基本單元,并作為獨立設計成果被交換、轉讓和銷售。

IP核對應描述功能行為的不同分為三類,即軟核(Soft IP Core)、固核(Firm IP Core)和硬核(Hard IP Core)。

當IP硬核是以芯片的形式提供時,就變成了Chiplet。

我們可以這么理解:SiP中的Chiplet就對應于SoC中的IP硬核,Chiplet 是一種新的 IP 重用模式,就是硅片級別的IP重用。

設計一個SoC系統級芯片,以前的方法是從不同的 IP 供應商購買一些 IP,軟核、固核或硬核,結合自研的模塊,集成為一個 SoC,然后在某個芯片工藝節點上完成芯片設計和生產的完整流程。有了Chiplet以后,對于某些 IP,就不需要自己做設計和生產了,而只需要買別人實現好的硅片,然后在一個封裝里集成起來,形成一個 SiP。

所以,Chiplet 可以看成是一種硬核形式的 IP,但它是以芯片的形式提供的。因此,我們稱之為IP芯片化。

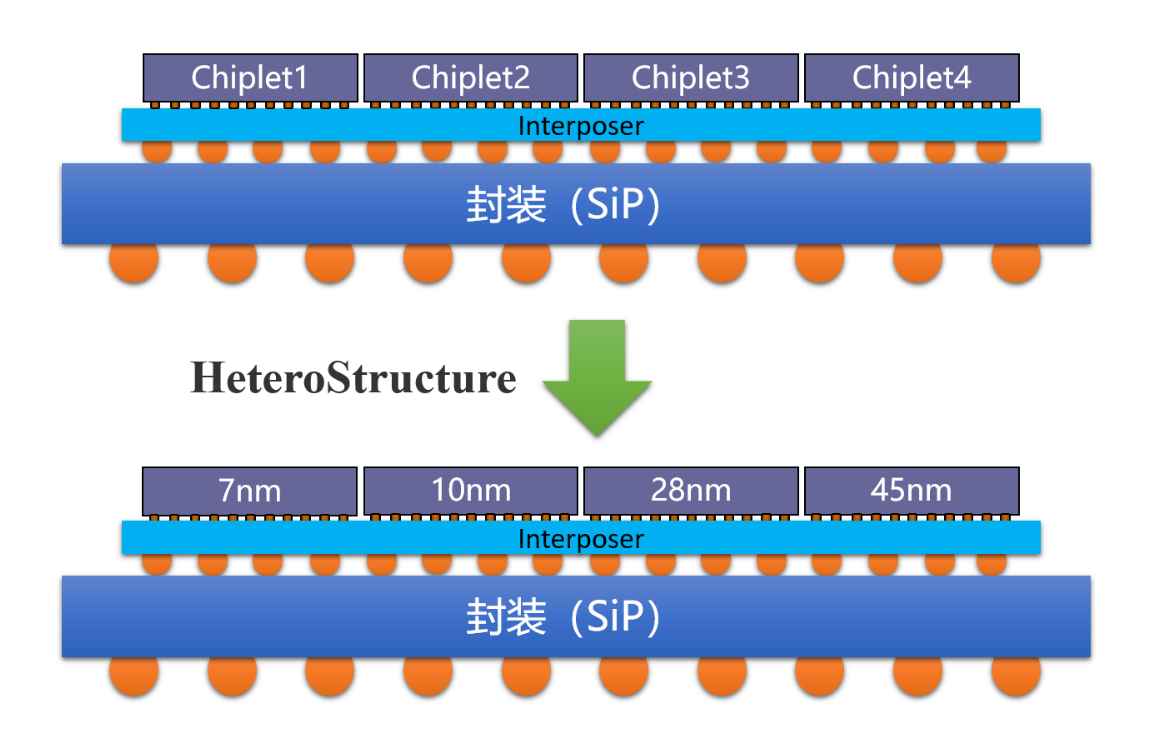

二、 集成異構化

在半導體集成中,Heterogeneous 是異構異質的含義,在這里我們將其分為異構HeteroStructure和異質HeteroMaterial兩個層次的含義。

HeteroStructure Integration

在這篇文章中,異構集成HeteroStructure Integration主要指將多個不同工藝單獨制造的芯片封裝到一個封裝內部,以增強功能性和提高工作性能,可以對采用不同工藝、不同功能、不同制造商制造的組件進行封裝。

例如上圖所示:將7nm、10nm、28nm、45nm的Chiplet通過異構集成技術封裝在一起。

通過異構集成技術,工程師可以像搭積木一樣,在芯片庫里將不同工藝的Chiplet小芯片組裝在一起。

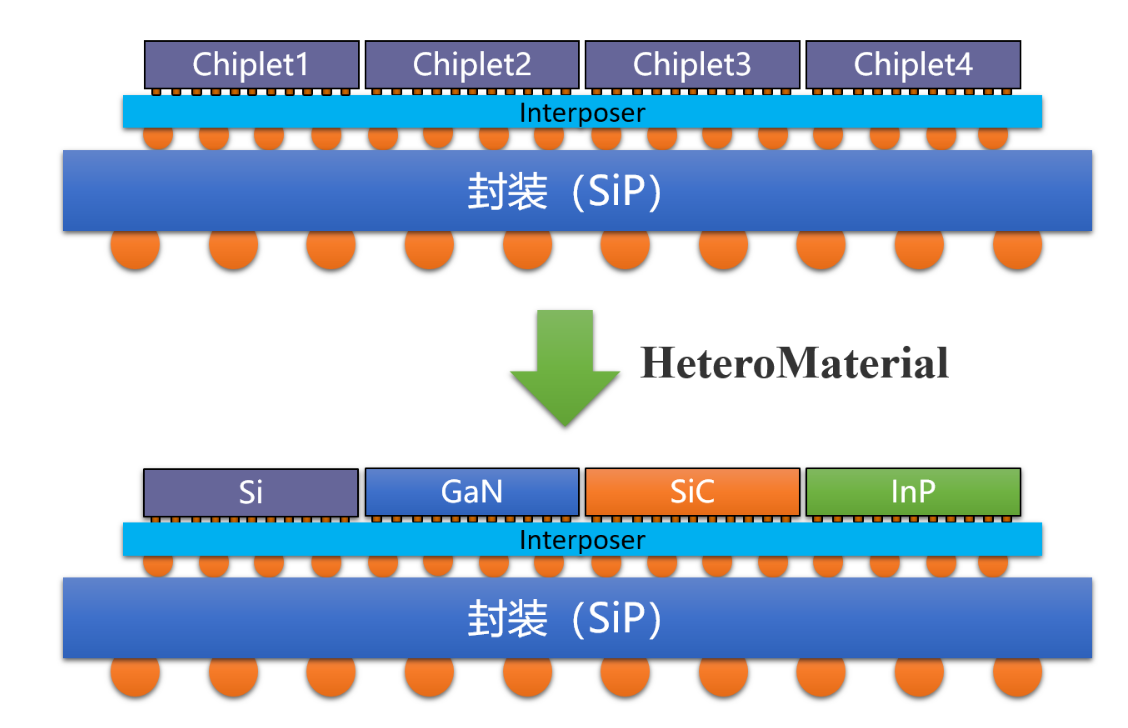

HeteroMaterial Integration

近年來集成硅(CMOS和BiCMOS)射頻技術已經在功率上取得巨大的進步,同時也將頻率擴展到了100GHz左右。然而還有眾多應用只能使用像磷化銦(InP)和氮化鎵(GaN)這樣的化合物半導體技術才能實現。磷化銦能提供最大頻率為1太赫茲的晶體管,具備高增益和高功率,以及超高速混合信號電路。而氮化鎵能使器件具備大帶寬、高擊穿電壓、以及高達100GHz的輸出頻率。

因此將不同材料的半導體集成為一體——即異質集成HeteroMaterial Integration,可產生尺寸小、經濟性好、設計靈活性高、系統性能更佳的產品。

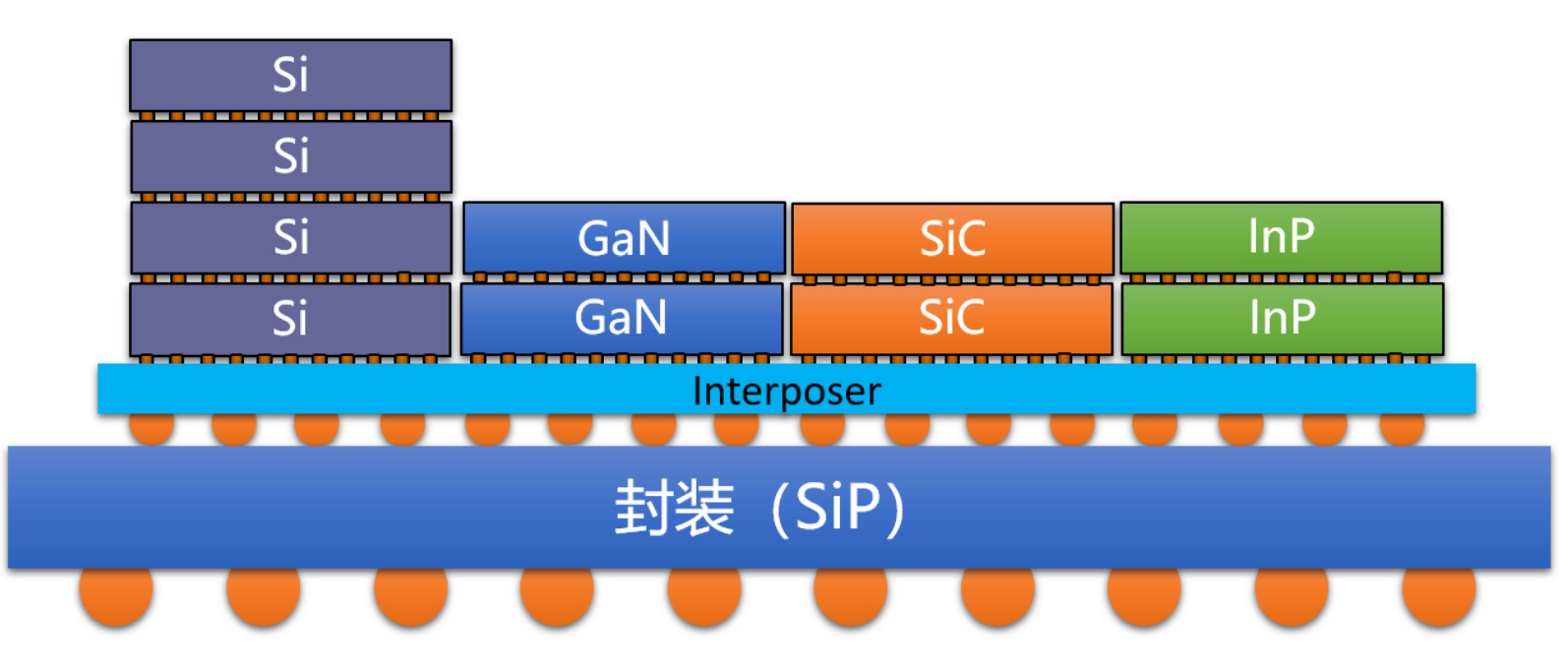

如下圖所示,將Si、GaN、SiC、InP生產加工的Chiplet通過異質集成技術封裝到一起,形成不同材料的半導體在同一款封裝內協同工作的場景。

在單個襯底上橫向集成不同材料的半導體器件(硅和化合物半導體)以及無源元件(包括濾波器和天線)等是Chiplet應用中比較常見的集成方式。

需要讀者注意的是,目前不同材料的多芯片集成主要采用橫向平鋪的方式在基板上集成,對于縱向堆疊集成,則傾向于堆疊中的芯片采用同種材質,從而避免了由于熱膨脹系統等參數的不一致而導致的產品可靠性降低,如下圖所示。

三、 IO增量化

如果說前面講的是Chiplet技術的優勢,那么,IO增量化則給Chiplet帶來了挑戰。

IO增量化體現在水平互聯(RDL)的的增量化,同時也體現在垂直互聯(TSV)的增量化。

在傳統的封裝設計中,IO數量一般控制在幾百或者數千個,Bondwire工藝一般支持的IO數量最多數百個,當IO數量超過一千個時,多采用FlipChip工藝。在Chiplet設計中,IO數量有可能多達幾十萬個,為什么會有這么大的IO增量呢?

我們知道,一塊PCB的對外接口通常不超過幾十個,一款封裝對外的接口為幾百個到數千個,而在芯片內部,晶體管之間的互聯數量則可能多達數十億到數百億個。越往芯片內層深入,其互聯的數量會急劇增大。

Chiplet是大芯片被切割成的小芯片,其間的互聯自然不會少,經常一款Chiplet封裝的硅轉接板超過100K+的TSV,250K+的互聯,這在傳統封裝設計中是難以想象的。

由于IO的增量化,Chiplet的設計也對EDA軟件提出了新的挑戰,Chiplet技術需要EDA工具從架構探索、芯片設計、物理及封裝實現等提供全面支持,以在各個流程提供智能、優化的輔助,避免人為引入問題和錯誤。

Cadence、Synopsys、Siemens EDA(Mentor)等傳統的集成電路EDA公司都相繼推出支撐Chiplet集成的設計仿真驗證工具。

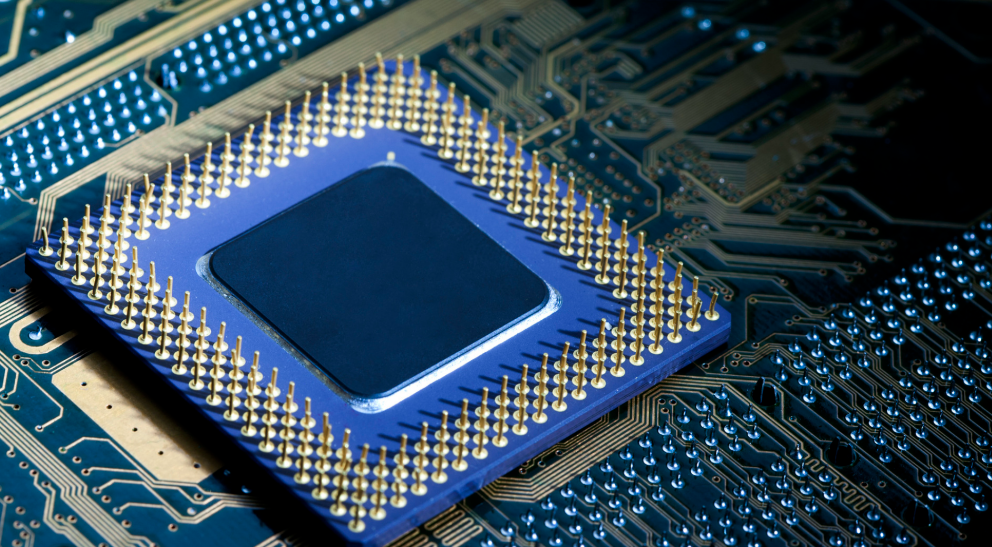

四、Chiplet芯粒先進芯片封裝清洗:

合明科技研發的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

水基清洗的工藝和設備配置選擇對清洗精密器件尤其重要,一旦選定,就會作為一個長期的使用和運行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環境中的濕氣,通電后發生電化學遷移,形成樹枝狀結構體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內的浮點、灰塵、塵埃等,這些污染物會導致焊點質量降低、焊接時焊點拉尖、產生氣孔、短路等等多種不良現象。

這么多污染物,到底哪些才是最備受關注的呢?助焊劑或錫膏普遍應用于回流焊和波峰焊工藝中,它們主要由溶劑、潤濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質在所有污染物中的占據主導,從產品失效情況來而言,焊后殘余物是影響產品質量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質引發接觸電阻增大,嚴重者導致開路失效,因此焊后必須進行嚴格的清洗,才能保障電路板的質量。

合明科技運用自身原創的產品技術,滿足芯片封裝工藝制程清洗的高難度技術要求,打破國外廠商在行業中的壟斷地位,為芯片封裝材料全面國產自主提供強有力的支持。

推薦使用合明科技水基清洗劑產品。

![[x]](/template/default/picture/closeimgfz1.svg)