因為專業

所以領先

近日,清華大學集成電路學院教授吳華強團隊研制出一顆新型芯片,能高效“片上學習”不少人工智能任務。這顆芯片的核心元器件是“憶阻器”,架構是“存算一體”,創新點在于能耗只有常規系統的3%,研究水平很高,2023年9月14日在線發表在《科學》上。

美國芯片產業出口管制的背景下,芯片話題自帶熱度,清華的這個高水平芯片成果,引發了不少人的興趣,希望看到中國芯片技術的新突破,但又感覺看不懂,這里我們需要關注“存算一體”、“憶阻器”以及“片上學習”這三個點,以及它們的協同一體化。

日常的編程,大多是在軟件層面進行,其中“軟硬件結合”、“嵌入式編程”指的是開發者能夠對傳感器、相機之類的硬件外設進行連接、SDK調用,但不需要知道硬件細節。

再深入,編程可以延伸到操作系統、指令集層面,這要求開發者對整個計算系統更為了解,用匯編語言之類的辦法或者繞開普通編程與界面工具的限制,直接對系統進行深層調用,進而提高效率,但這還是在軟件層面,思維都是基于0-1數值邏輯的。

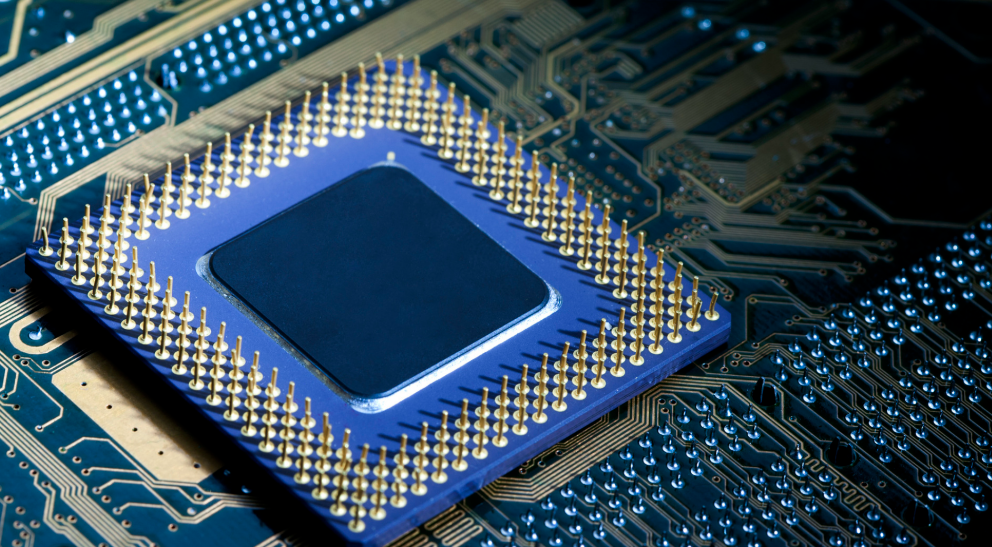

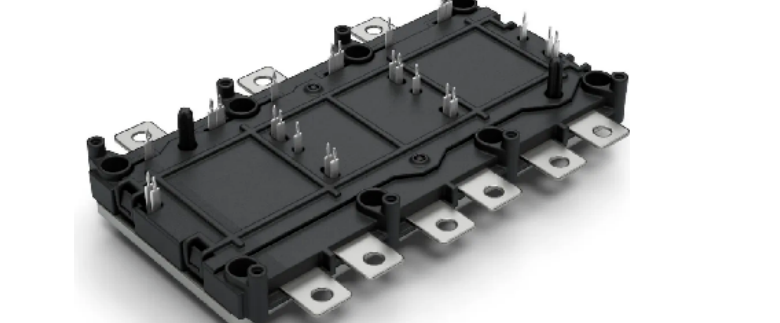

繼續深入,就涉及到到芯片層面。由于芯片和系統架構決定了計算系統的特性,有一定實力的公司會直接使用芯片進行開發,甚至自研復雜的芯片。目前階段,制造芯片與傳統IT產業01邏輯有區別,更像是一個在硅片上以納米尺度繡花的物理化學過程,它的基礎是半導體元器件。所以,芯片設計,是IT業真正“軟硬兼修”的連接環節。它一頭要理解指令集、操作系統、程序邏輯、人工智能等軟件知識,一頭又要和元器件、芯片架構等底層硬件知識打交道。

近年來,由于神經網絡、深度學習的流行,業界在芯片設計層面對神經網絡的研究也很熱門。清華的憶阻器芯片,就是把以上各類知識綜合到一起,深入理解之后的創新。在這個層面,如何存儲、更新數據,都需要深入思索,并作出創新。

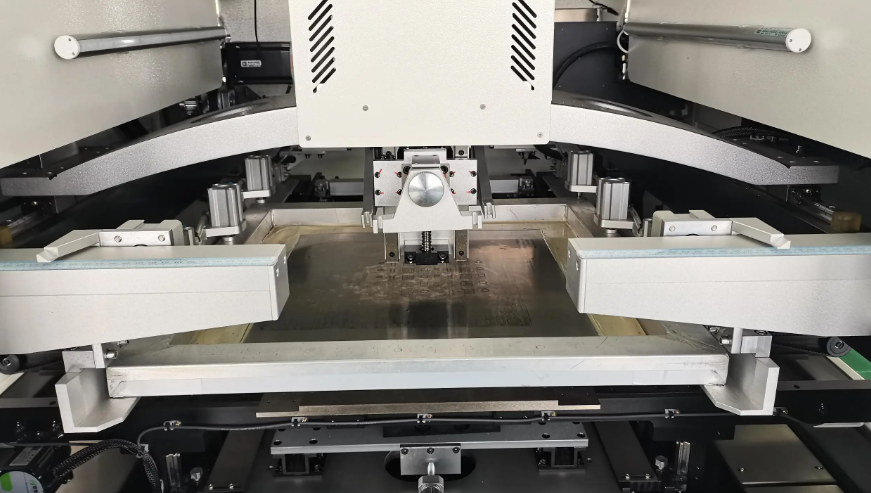

雖然憶阻器與交叉陣列展現了潛在的性能,但是要實際做出芯片應用,體現憶阻器的優點,還是個相當有挑戰性的事——這需要對機器學習算法、系統架構、元器件設計、芯片設計、芯片制造都有相當的了解,才能做出完整的驗證系統。而清華作者們就是具體實現了一個基于憶阻器交叉陣列的新架構芯片,能算是完全集成(fully integrated)的憶阻器芯片,并通過一系列人工智能任務上展現了芯片架構的優點與潛力。

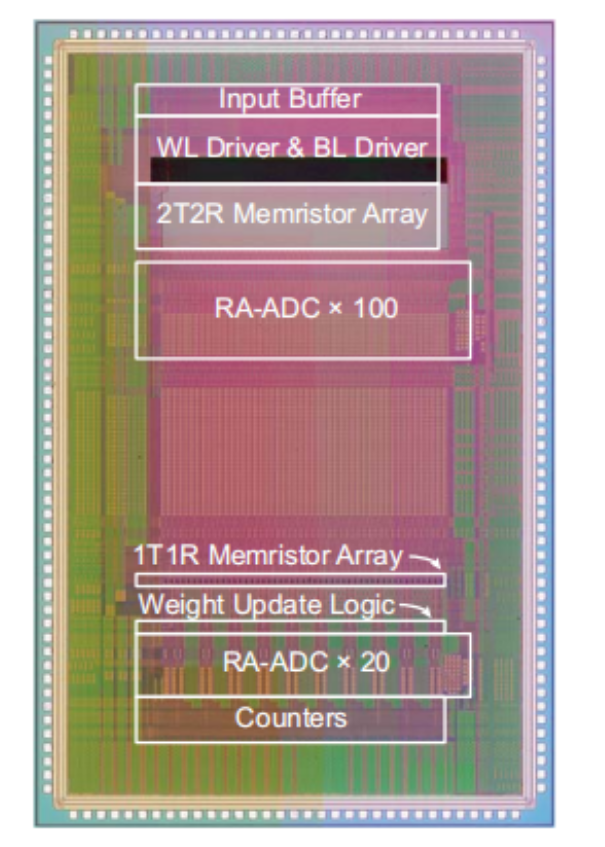

清華團隊開發的憶阻器芯片架構叫STELLAR,有兩個憶阻器交叉陣列數組,大一些的是2T2R的,有1568*100個憶阻器,在神經網絡模型中代表784*100的權重矩陣。小一些的是1T1R的,有100*20個憶阻器,代表100*10的權重矩陣(注意不是100*20)。兩個憶阻器交叉陣列組合成了784*100*10的一個三層神經網絡結構,用于完成一些小型的人工智能算法任務。

這兩個Crossbar各有特性。大的是2T2R的,里面的權重是“off-chip”離線訓練好的,然后上傳到交叉陣列里面,它的特點是可以并行計算矩陣乘法,節點數多,展現了“存算一體”的優良特性。小的是1T1R的,規模小,但是后面附帶權重更新邏輯,可以在芯片內訓練更新網絡權重,展現了“片上學習”(on-chip learning)的功能。

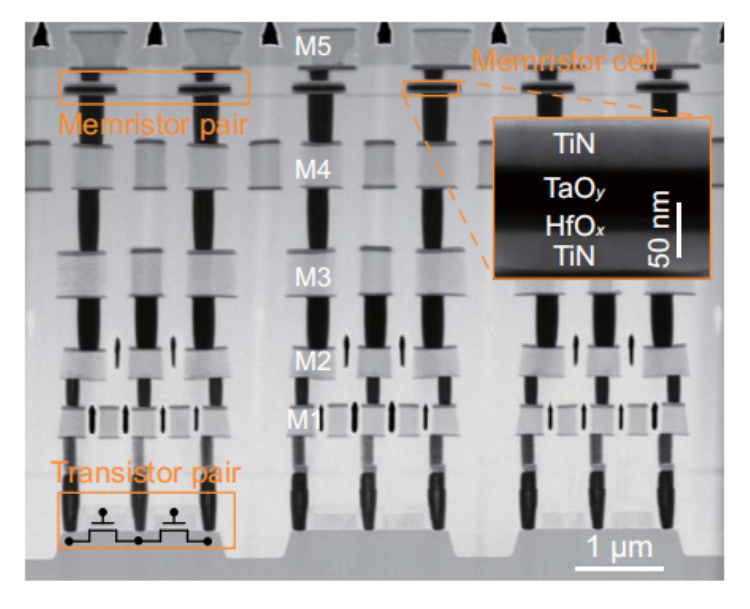

兩個憶阻器交叉陣列結合CMOS芯片制造工藝,真的造出來了,上圖是2T2R Crossbar的局部切片圖。這個生產工藝良率接近100%,切片圖像清晰。憶阻器元器件的制造應該不是難題了,材料也從二氧化鈦變成了幾種物質復合,元器件性能應該還有提升空間。

芯片上面也是有許多CMOS晶體管的,有輔助核心模塊的周邊電路,處理神經網絡前向推導、反向傳播學習的邏輯。還有ADC轉換,將兩個憶阻器交叉陣列的模擬物理量輸出轉換成數字。應用這顆芯片,其實就是用里面兩個權重矩陣的推理與訓練功能。

這芯片可以獨立地作為一個神經網絡運作,也可以在外面再加上一些層,作為網絡的一部分。如實現CNN網絡時,前面需要在外接電腦上實現一些卷積層,用這兩個矩陣當最后的全連接層輸出。

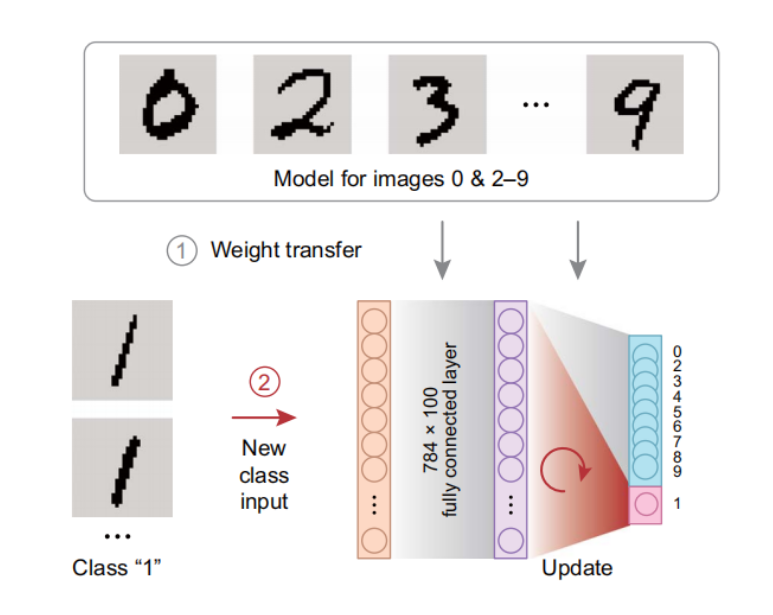

測試與訓練時,需要外接的設備對這芯片傳入數據、接收結果。整個測試體系搭建起來后,就是一個完整的系統,可以對芯片的性能進行完整的測試。測試的神經網絡功能相對簡單但能展現特性,例如,輸出是10個節點,正好對應0-9的10個數字,可以用來測MINST數據集里的手寫數字識別。

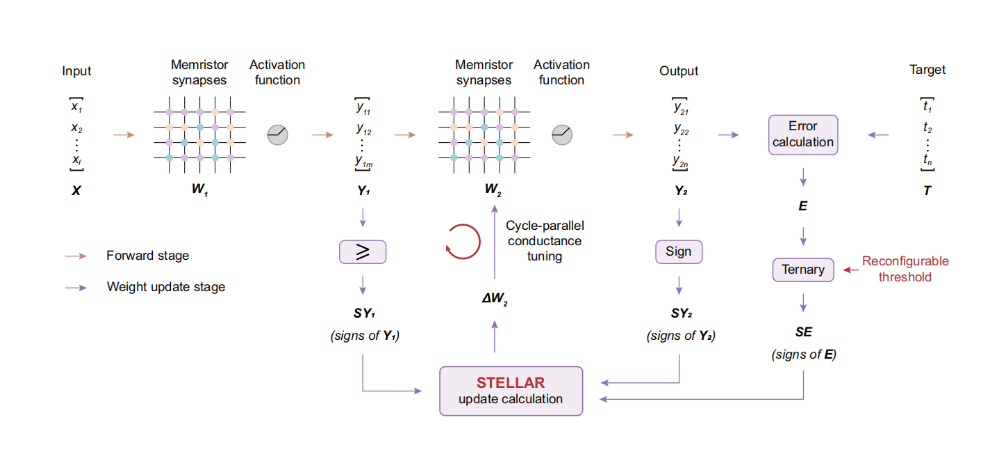

芯片架構叫STELLAR,是“sign- and threshold-based learning”的簡稱,指的是訓練中的創新。如上圖,W1是大的交叉陣列,輸入向量X進來,乘以矩陣W1,再用激活函數(Activation function)ReLU變換——其實很簡單,負數變0,正數不變——變成向量Y1。Y1再乘以矩陣W2,再ReLU變換,成為輸出向量Y2。Y2與訓練樣本T比較,生成誤差向量E。

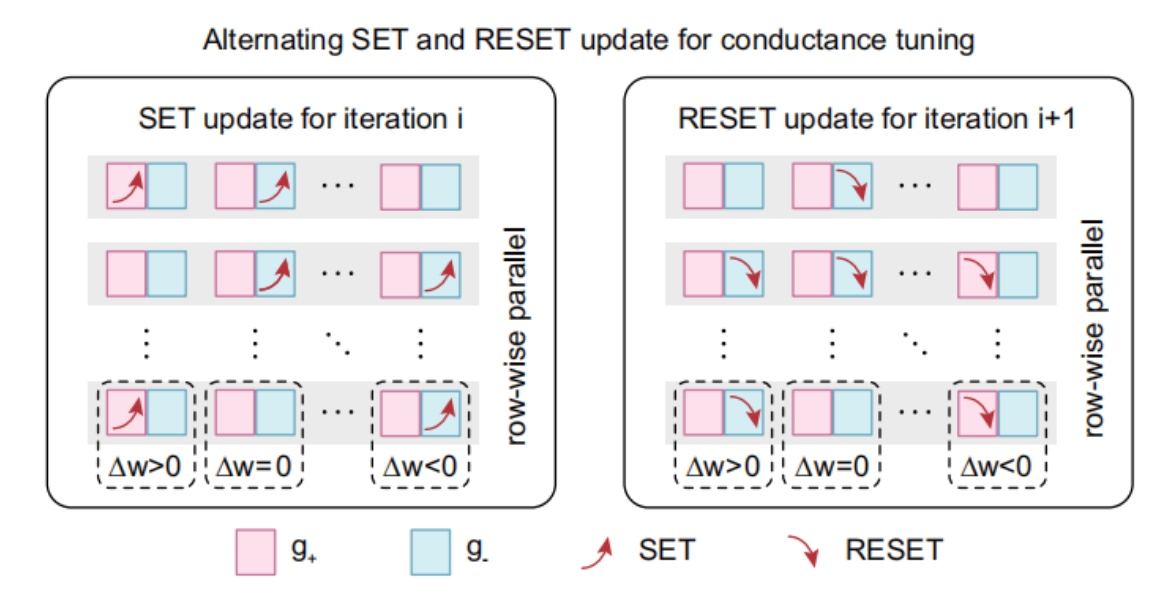

清華團隊的創新是,對W2的訓練,先將Y1、Y2、E三個向量的符號抽出來,實施更好的權重更新辦法。其出發點是,一個權重是用一正一負兩個憶阻器存儲的,可以選擇性根據符號,一列一起更新。這是深入思考反向傳播的權重更新算法,結合元器件架構,實現了憶阻器潛在的并行功能。如圖,權重更新分為SET和RESET兩個步驟,SET步驟只對正的符號更新正Cell,對負的符號更新負Cell,而RESET正相反。這樣SET和RESET分別都可以按列并行加速了。

另一個創新是,在誤差向量E上加一個threshold,預先將一些微小的誤差過濾掉,這樣給出的符號向量,訓練性能更優。這個threshold是可配置的,對不同的網絡模型可以設置相應的過濾門限值,這應該是結合SET和RESET特性的進一步優化。

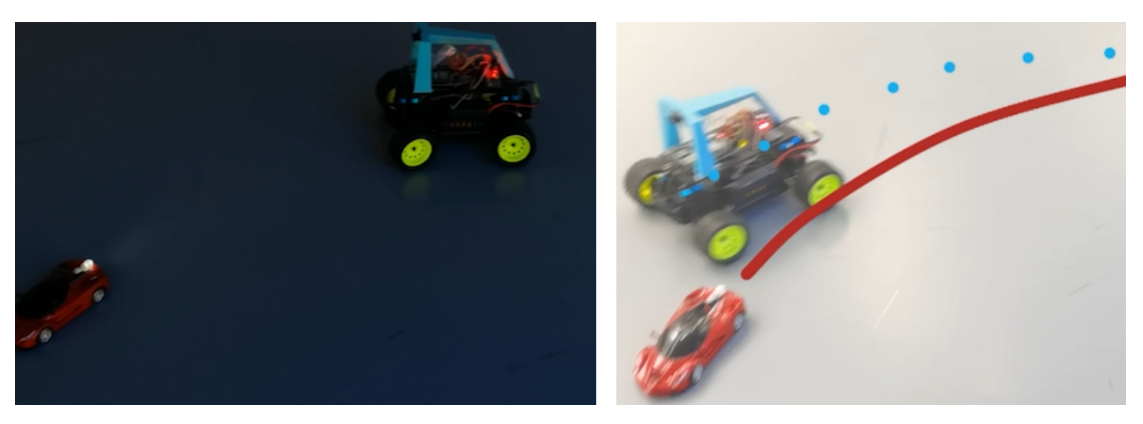

這個STELLAR架構,是為展現高效的片上學習功能。清華團隊進行了多項測試,如追逐光點的運動小車。光點在前面一個車的尾燈上,后面的運動小車用攝像頭拍前面的圖像,用憶阻器芯片計算決定操控動作。夜晚的追光功能用CNN網絡事先訓練好了,前6個卷積層在PC上實現,后面512*100*10的兩個全連接層權重轉移到兩個憶阻器交叉陣列上了。

實驗表明,晚上跟尾燈表現不錯。但是白天因為沒訓練,就追得不好。收集白天圖像,對后一個1T1R的憶阻器交叉陣列進行“片上學習”。只要100次訓練就有大幅提升,白天也能跟好了,同時晚上也還是能更好。

另一個實驗是,事先將識別數字0、2-9的9個數字的網絡訓練好,784*100*10的網絡權重轉移到憶阻器芯片里(正好全用上了),故意不訓練數字1。之后再把1的樣本放上來,對后一個憶阻器交叉陣列進行訓練,只要100個樣本,1也能認了,識別率從7%提升到93%,老的數字識別率只是從95.3%微降到93.2%,這說明芯片能適應新類型的學習樣本。

還有語音識別演示,女聲提前訓練好,男聲在片上學習,也能學成。還通過ResNet網絡的例子,展示了架構的可擴散性。這些人工智能任務,以及網絡架構,按現在的深度學習進展來看,都是較為基礎的(都還算是實用),但是用憶阻器芯片來演示展現特性,是文章的創新。

在字符識別測試時,清華團隊還用48天進行了重復測試,結果是穩定的。這說明憶阻器芯片里的權重是穩定的,這是芯片能實用的重要特性。

可以看出,這顆憶阻器芯片是真的有“存算一體”的特性。矩陣權重就在芯片里,計算過程也是在芯片里完成的,而且還有神經形態處理器的仿生特性。

通過STELLAR架構并行加速等創新,相對專用集成電路(ASIC)加速的常規系統,清華團隊實現了35倍的能耗效率,這是芯片架構的突出亮點。STELLAR架構里,不需要高能耗的write verification,在能耗效率上非常有優勢。而且這是一顆相對完整獨立的憶阻器芯片,較為系統地展示了憶阻器在神經網絡計算方面的潛力,對于邊緣計算有突破性意義。

通過以上的介紹,我們再看新聞通稿的內容,就會明白多了(以下為通稿原文):

● 全球首顆全系統集成的、支持高效片上學習(機器學習能在硬件端直接完成)的憶阻器存算一體芯片,在支持片上學習的憶阻器存算一體芯片領域取得重大突破。

● 該芯片有望促進人工智能、自動駕駛、可穿戴設備等領域發展。

● 芯片包含支持完整片上學習所必需的全部電路模塊,成功完成圖像分類、語音識別和控制任務等多種片上增量學習功能驗證,展示出高適應性、高能效、高通用性、高準確率等特點,有效強化智能設備在實際應用場景下的學習適應能力。

● 相同任務下,該芯片實現片上學習的能耗僅為先進工藝下專用集成電路(ASIC)系統的3%,展現出卓越的能效優勢,極具滿足人工智能時代高算力需求的應用潛力,為突破馮·諾依曼傳統計算架構下的能效瓶頸提供了一種創新發展路徑。

通過以上的討論也能看出,清華憶阻器芯片主要還是在性能探索層面,大規模進入工業實用還需要進一步優化。因為基于常規芯片的人工智能系統已經大規模應用了,深度學習取得突破后,識別性能相當好,一些應用成本很低。

目前來看,憶阻器芯片能夠承載的網絡規模還是有限,識別的準確率只是90%多,離100%還有不小的距離,和工業應用的高可靠性標準還是有點差距。一些復雜應用使用了規模很大的深度神經網絡DNN,憶阻器交叉陣列只能在里面占部分環節,整個應用還是需要以傳統的馮·諾依曼結構為基礎。

也就是說,簡單的神經網絡應用,傳統的架構已經夠好,能耗和成本都夠低。復雜的應用,傳統架構是有“馮·諾依曼瓶頸”,能耗高很需要改進,憶阻器芯片現階段還不足以在復雜應用中充分發揮作用。但是,憶阻器芯片確實展現出了并行加速與高效存儲的特性,這讓人很感興趣,相信未來會有更多進展。

![[x]](/template/default/picture/closeimgfz1.svg)