因為專業

所以領先

近些年,先進封裝已經成為半導體中越來越普遍的主題,那么半導體先進封裝是什么?首先要知道半導體封裝是指將生產加工后的晶圓進行切割、焊線、塑封,使電路與外部器件實現連接,并為半導體產品提供機械保護,使其免受物理、化學等環境因素損失的工藝。

隨著先進制程工藝逐漸逼近物理極限,包括臺積電在內的廠商已經開始將研發方向由先前的“如何把芯片變得更小”轉變為“如何把芯片封得更小”,先進封裝逐漸成為行業發展重點。

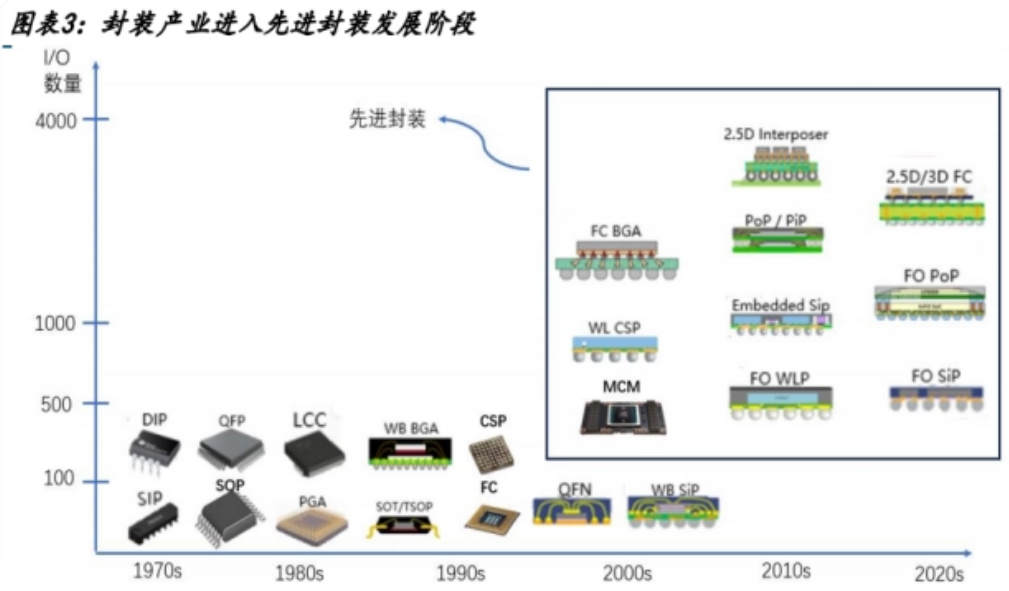

目前半導體封裝技術正在從傳統封裝(SOT、QFN、BGA等)向先進封裝(FC、FIWLP、FOWLP、TSV、SIP等)轉型。先進封裝作為提高連接密度、提高系統集成度與小型化的重要方法,在單芯片向更高端制程推進難度大增時,擔負起延續摩爾定律的重任。

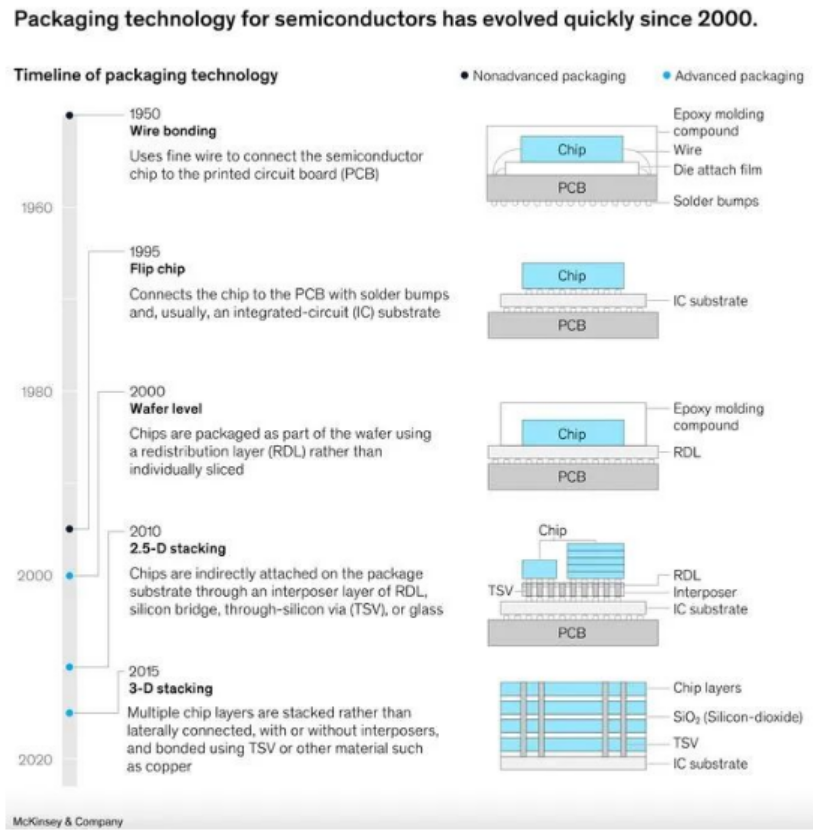

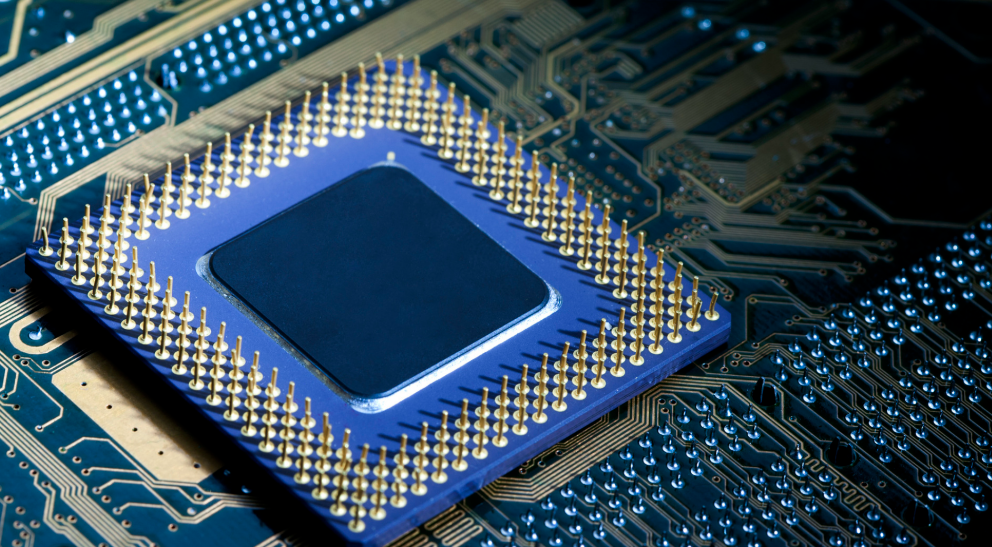

自20世紀90年代中期之后,集成電路封裝體的外觀(形狀、引腳樣式)并未發生重大變化,但其內部結構發生了三次重大技術革新:引線鍵合(Wire Bonding)、倒裝封(Flip Chip)和晶圓級封裝(WLCSP,Wafer Level Chip Scale Package)。

封裝技術的發展史是芯片性能不斷提高、系統不斷小型化的歷史。根據《中國半導體封裝業的發展》,半導體封裝技術的發展歷史可大致分為以下五個階段:

第一階段:20 世紀 70 年代以前(通孔插裝時代),封裝技術是以 DIP 為代表的針腳插裝,特點是插孔安裝到 PCB 板上。這種技術密度、頻率難以提高,無法滿足高效自動化生產的要求。

第二階段:20 世紀 80 年代以后(表面貼裝時代),用引線替代第一階段的針腳,并貼裝到PCB 板上,以 SOP 和 QFP 為代表。這種技術封裝密度有所提高,體積有所減少。

第三階段:20 世紀 90 年代以后(面積陣列封裝時代),該階段出現了 BGA、CSP、WLP為代表的先進封裝技術,第二階段的引線被取消。這種技術在縮減體積的同時提高了系統性能。

第四階段:20 世紀末以后,多芯片組件、三維封裝、系統級封裝開始出現。

第五階段:21 世紀以來,主要是系統級單芯片封裝(SoC)、微機電機械系統封裝(MEMS)。

圖片來自于國金證券

半導體先進封裝的兩個方向:

1、小型化:3D封裝突破傳統的平面封裝的概念,通過單個封裝體內多次堆疊,實現了存儲容量的倍增,進而提高芯片面積與封裝面積的比值。

2、高集成:系統級封裝SiP能將數字和非數字功能、硅和非硅材料、CMOS和非CMOS電路以及光電、MEMS、生物芯片等器件集成在一個封裝內,在不單純依賴半導體工藝縮小的情況下,提高集成度,以實現終端電子產品的輕薄短小、低功耗等功能,同時降低廠商成本。

Chiplets——小芯片!目前也是各大廠商研發重點,將大籌碼分成許多小籌碼。同樣是高集成的解決方案。

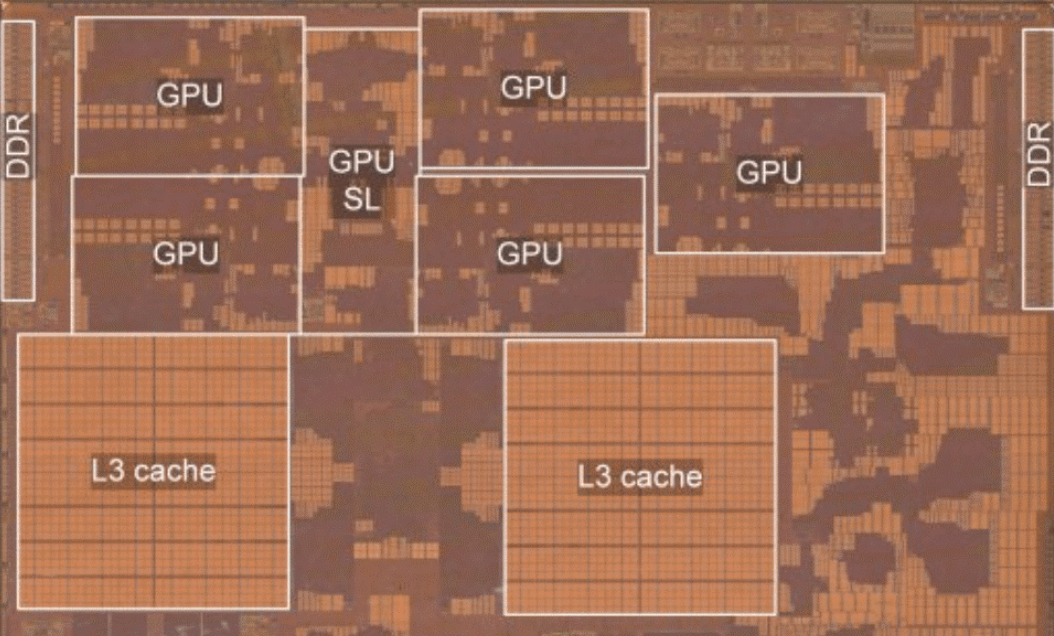

AMD 是這方面最受歡迎的例子,但這是整個行業的趨勢。AMD 可以設計 3 個芯片,一個CPU 核心小芯片和2 個 IO 芯片。這 3 種設計覆蓋了很大一部分市場。同時,英特爾設計了 2 個 Alder Lake 臺式機芯片和 3 個 Ice Lake 服務器芯片,以服務于相同的潛在市場。因此,AMD 可以節省設計成本,制造比英特爾更多內核的 CPU,并節省收益成本。

小芯片(Chiplet)很棒,但它不是孤立的解決方案。也會遇到許多問題。每個晶體管的成本仍在上升,設計成本飆升,由于需要更多 IO 來與其他芯片接口,小芯片被pad限制。由于 IO 限制,部分芯片無法拆分,因此芯片尺寸仍在達到峰值。

那么行業解決辦法是什么?

先進封裝!

這就是我們要注意的地方,一些工具供應商將所有倒裝芯片封裝稱為“先進封裝”。SemiAnalysis 和大多數業內下游人士不會這么說。因此,我們將所有凸點尺寸小于100 微米的封裝稱為“先進”。

最常見的先進封裝類別稱為扇出。有些人會爭辯說它甚至不是先進的封裝,但那些人大錯特錯。以Apple 為例,他們將讓臺積電采用應用處理器芯片,并將其與 90 微米到 60 微米數量級的更密集凸塊封裝到重組或載體晶圓/面板上。與傳統倒裝芯片封裝相比,凸點密度大約高出 8 倍。

這種重組或載體晶圓/面板然后進一步展開 IO,因此得名扇出。然后將扇出封裝連接到主板。硅芯片的設計可以減少對pad受限的擔憂,因為扇出處的pad較小。該封裝還可以封裝 DRAM 內存、NAND 存儲和PMIC。集成扇出不僅有利于密度,而且它們還在封裝上保留了大量的芯片間 IO。否則,該 IO 將不得不以更大的IO 間距尺寸通過主板進行接口。

集成扇出對于高性能應用程序變得越來越普遍,不僅僅是移動應用程序。增長最快的用例是在十多年來設計一直受到限制的事物的網絡方面。AMD 將在其服務器 CPU 和 GPU中非常積極地采用扇出。Tesla Dojo 1是集成扇出封裝的另一個引人注目的例子,但在晶圓級。SemiAnalysis透露,特斯拉將在發布公告前使用這種包裝類型。

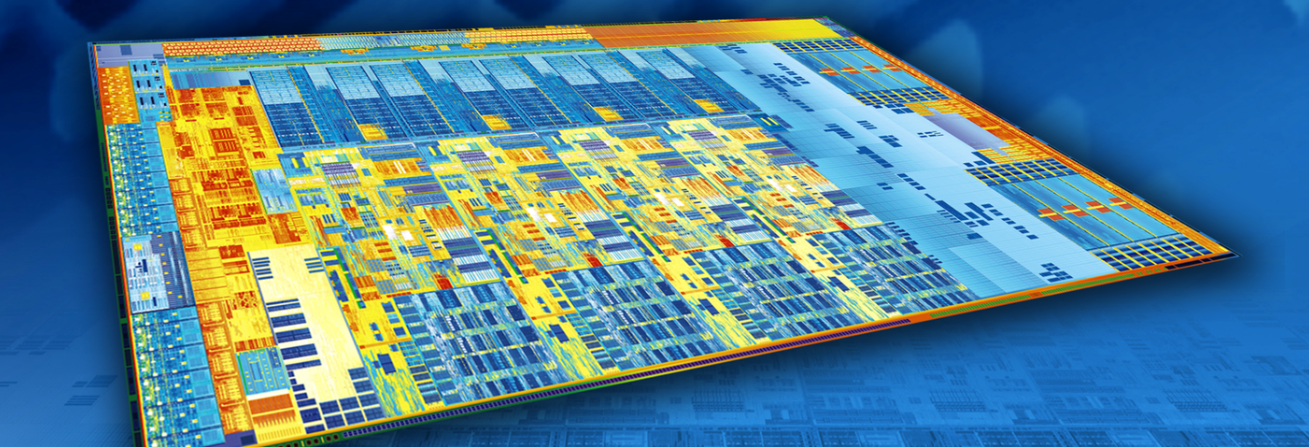

在先進封裝中,有 2.5D 和 3D 封裝。2.5D 涉及封裝在其他硅片上的硅片,但較低的硅片專用于布線,沒有有源晶體管。這通常以55 微米到 50 微米的間距完成,因此凸點密度高出約 16 倍。最常見和最高容量的用例是具有 TSMC CoWoS(基板上晶圓上芯片)的 Nvidia 數據中心 GPU。臺積電將有源芯片封裝在只有互連和微凸點的晶圓上。然后使用傳統方法將這疊芯片封裝到基板上。

其他示例基本上包括每個帶有 HBM 的處理器。HBM 是作為一種階梯函數增加內存帶寬的方法而建立的,這種方法高于傳統形式的 DRAM。它通過使用更寬的內存總線來實現這一點。這些寬總線會產生與 IO 計數相關的問題,但 HBM 是從頭開始設計的,以便在同一包內共存。這顛覆了 IO 問題,同時也允許更緊密的集成。

2.5D 的更多示例包括基于Intel EMIB 的產品、Xilinx FPGA、AMD 最新的數據中心 GPU 和Amazon Graviton 3.

3D 封裝將一個有源芯片封裝在另一個有源芯片之上。這最初是由英特爾提供的55 微米間距的邏輯硅片,但批量用例將是 36 微米或更小。臺積電和 AMD 將推出 17 微米間距的 3d堆疊 V-cache。該技術從凸塊轉移到硅通孔 (TSV),并且具有更大的擴展空間。

索尼制造的 CMOS 圖像傳感器等其他應用已經采用 6.3 微米間距。為了繼續進行比較,36 微米間距的凸塊密度高 31 倍,以17 微米間距實現的銅 TSV 的 IO 密度高 138 倍,索尼的 6.3 微米間距的CMOS 圖像傳感器的 IO 密度高 567 倍標準倒裝芯片。

先進封裝的出現,讓業界看到了通過封裝技術推動芯片高密度集成、性能提升、體積微型化和成本下降的巨大潛力。目前,人工智能(AI)、高性能計算、數據中心、自動駕駛汽車、5G都有先進封裝的身影,應用領域逐漸擴大,各大廠商摩拳擦掌地為AI浪潮積極地做準備,一場先進封裝技術競賽已然拉開了帷幕。

下一篇:助焊劑殘留物清洗

![[x]](/template/default/picture/closeimgfz1.svg)