因為專業

所以領先

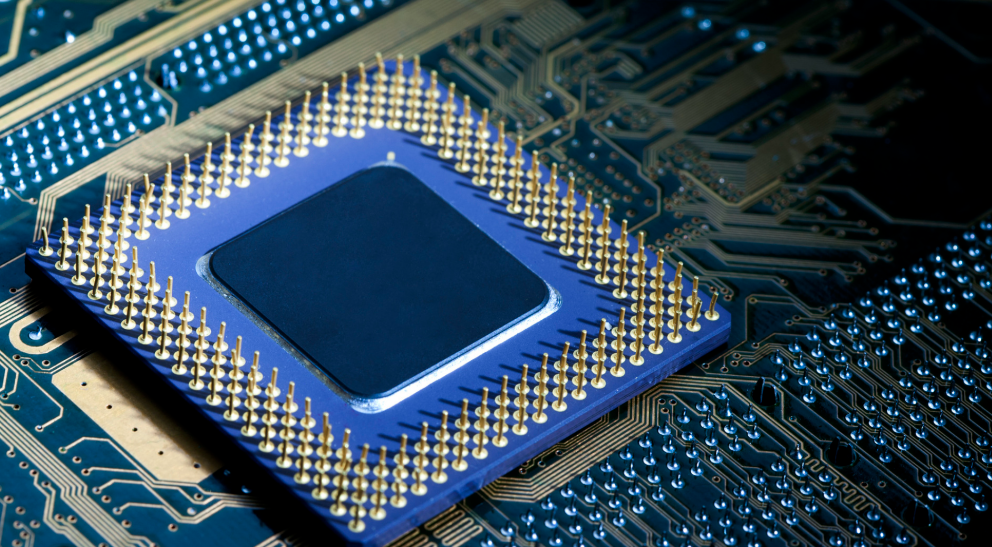

3D功能封裝技術,又稱為疊層芯片封裝技術,是一種在不改變封裝體尺寸的前提下,于同一個封裝體內垂直方向疊放兩個以上芯片的封裝技術。

傳統的芯片封裝多是在二維平面上進行,隨著芯片技術發展,面臨著一些挑戰。例如,隨著芯片功能不斷增加,芯片面積增大,按照傳統方式制造大芯片會面臨良率、復雜工藝等難以調和的矛盾。3D封裝技術則將原本需要一次性流片的大芯片拆分成若干小面積的芯片(這些小芯片被稱為Chiplet),再通過先進的封裝工藝(硅片層面的封裝)將這些小芯片組裝成一顆大芯片,從而實現大芯片的功能和性能。

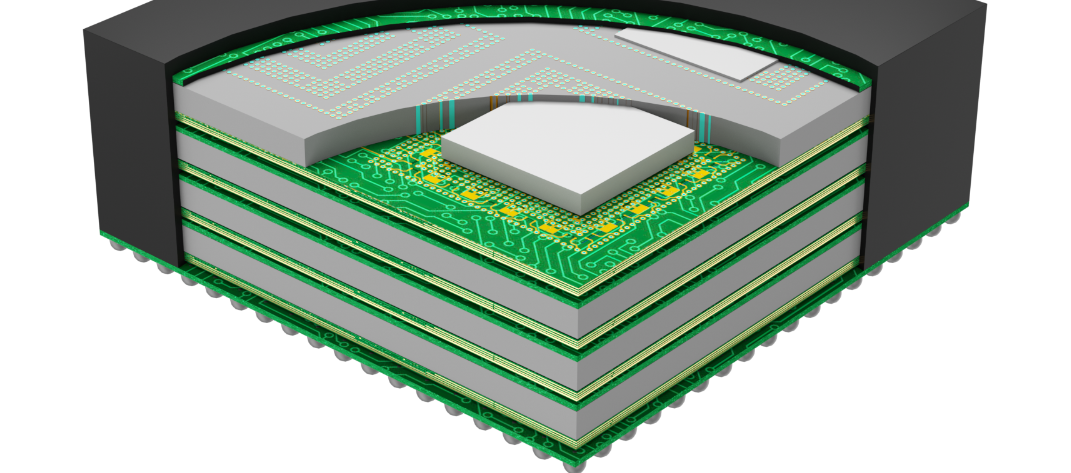

它與2.5D封裝技術有所不同。2.5D是在二維平面上,基于硅中介層(Interposer)將Chiplet組成一個大芯片,Chiplet之間在硅中介層上通過數據交互形成系統級芯片;而3D封裝是在三維空間組裝芯片,垂直方向堆疊更多小芯片以集成更多功能。例如在3D封裝結構中,像HBM(High Bandwidth Memory)寬帶存儲顆粒與下面的Die(裸片)之間可以通過微凸塊(Microbump)不斷往上堆疊多層,層與層之間通過硅穿孔(TSV,Through -Silicon -Via)來打通硅襯底,使得信號能在垂直方向(z方向)傳輸,并且為了實現不同層間高速io、GPU、CPU或者SoC的Die之間的連通(這些Die基本采用先進節點制作,Pitch間距比較小),還需要通過再分布層(RDL)在左右xy方向上進行信號拉通,最后將所有東西集成到封裝基板上,其下面還有不含有晶體管的Interposer硅載板。

3D功能封裝技術在眾多領域有著廣泛的應用。

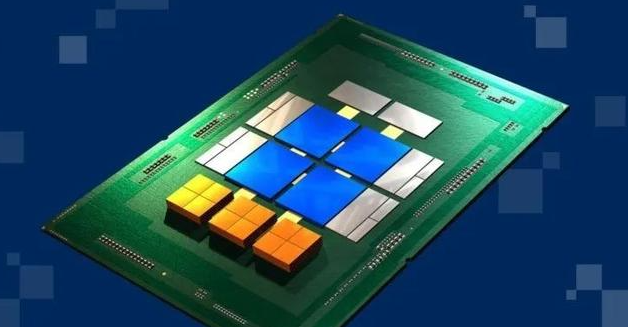

(一)高性能計算領域 在高性能計算方面,如CPU和GPU等核心計算芯片的封裝。以AMD為例,AMD的霄龍(EPYC)處理器系列通過3D封裝技術集成不同工藝的芯片,如io Die采用14nm的成熟工藝,CPU采用7nm最新工藝,這樣集成不同工藝的芯片大幅提高了芯片的良率,并且在每一個CPU Die上集成額外的Level 3緩存(Cache)提升了處理器性能。英特爾推出的Ponte Vecchio芯片,通過5種不同工藝將超過1000億個晶體管、47顆小芯片集成到一顆大芯片上,展現出3D封裝在高性能計算芯片上集成眾多功能模塊的能力。

(二)人工智能領域 人工智能算法對計算能力和數據處理速度要求極高。3D封裝技術能夠在有限的空間內集成更多的處理單元和存儲單元,加速數據的傳輸和處理。例如在一些AI芯片中,可以將多個計算核心與大容量的高速緩存或內存通過3D封裝緊密結合在一起。通過垂直堆疊芯片,可以縮短信號傳輸距離,提高數據傳輸帶寬,從而滿足人工智能應用對大量數據的快速處理需求。

(三)智能手機領域 隨著智能手機功能不斷增強,對芯片性能、功耗和空間利用的要求也越來越高。3D封裝技術有助于在更小的空間內集成更多功能的芯片。例如集成處理器、圖形處理單元、調制解調器以及各種傳感器芯片等。通過3D封裝,可以提高芯片集成度,減少手機主板空間占用,同時也有助于降低功耗,延長電池續航時間。

(四)汽車電子領域 汽車電子系統對芯片的可靠性、安全性和高性能有著嚴格要求。3D封裝技術可以將不同功能的芯片(如汽車的控制芯片、傳感器芯片、通信芯片等)集成在一起。一方面提高了系統的集成度,減少了布線長度和連接點,從而提高了系統的可靠性;另一方面,也有利于實現汽車電子系統的小型化和輕量化,滿足汽車行業對于電子設備空間和重量的限制要求。

3D封裝技術能夠顯著提高芯片的性能。通過垂直堆疊芯片,可以大大縮短芯片之間的信號傳輸距離,減少信號延遲。例如在高性能計算中,CPU和GPU之間或者芯片內部不同功能模塊之間的通信,如果采用3D封裝,信號傳輸路徑更短,數據交換速度更快。并且由于可以集成更多的功能模塊在一個封裝內,能夠實現更復雜的功能,如AMD在霄龍處理器中集成更多緩存來提升性能。

可以在不改變封裝體尺寸的情況下,在垂直方向堆疊多個芯片,使得在有限的空間內集成更多的功能。這對于空間要求嚴格的設備(如智能手機、可穿戴設備等)非常重要。能夠將多個不同功能的芯片(如計算芯片、存儲芯片、傳感器芯片等)集成到一個封裝體中,減少了整個系統的體積和重量,提高了設備的便攜性和集成度。

在一定程度上可以降低成本。對于一些不需要最先進工藝的功能模塊,可以采用成熟工藝制造的小芯片(Chiplet),然后通過3D封裝技術集成在一起,避免了整個大芯片都采用昂貴的先進工藝生產。例如,在一個包含多種功能的大芯片中,部分功能模塊對工藝要求不高,采用成熟工藝制造小芯片后再進行3D封裝,降低了生產成本。同時,由于提高了集成度,減少了芯片之間的連接線路等,也有助于降低制造成本。

便于根據不同的應用需求進行功能擴展和定制。可以靈活地選擇不同功能的小芯片進行堆疊封裝,滿足多樣化的市場需求。比如針對不同性能要求的服務器芯片,可以通過調整堆疊的小芯片數量、類型(如計算核心數量、緩存大小等)來實現不同的性能等級。

由于多個芯片在垂直方向緊密堆疊,芯片的散熱變得更加困難。芯片在工作過程中會產生熱量,而3D封裝結構使得熱量難以快速散發出去,容易導致芯片溫度過高。過高的溫度會影響芯片的性能和可靠性,甚至可能導致芯片損壞。例如在高性能計算場景下,長時間高負載運行時,3D封裝的芯片如果散熱措施不到位,就會出現性能下降甚至故障的情況。

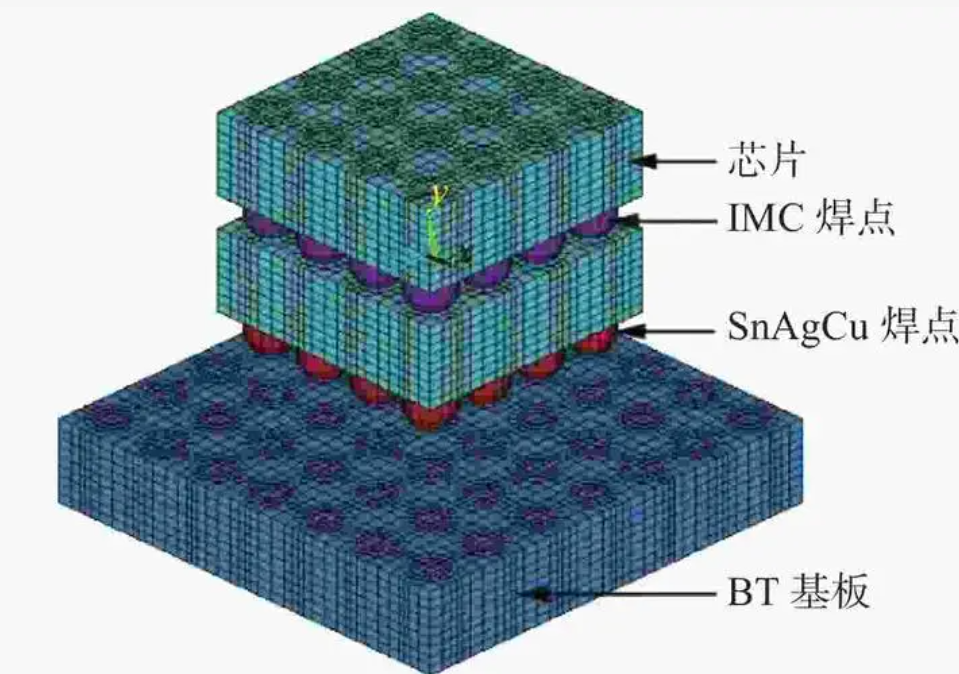

3D封裝技術的設計和制造過程相對復雜。在設計方面,需要考慮如何合理布局各個小芯片,確保信號傳輸的完整性、電源分配的合理性等。例如在垂直堆疊芯片時,要考慮不同層芯片之間的信號互連方式、信號干擾等問題。在制造方面,涉及到高精度的芯片堆疊、硅穿孔(TSV)制作、微凸塊(Microbump)連接等工藝,這些工藝的要求很高,增加了制造的難度和成本。

由于3D封裝結構的復雜性,芯片的測試變得更加困難。傳統的測試方法可能無法滿足3D封裝芯片的測試需求。例如,在測試垂直堆疊芯片內部的某個小芯片時,由于周圍芯片的遮擋和信號干擾等因素,很難準確地對其進行功能和性能測試。而且在封裝完成后,如果發現某個小芯片存在問題,修復和更換的難度也很大。

首先要將大芯片切割成小的Chiplet。這些Chiplet可以根據功能需求采用不同的工藝制造。例如在AMD的案例中,霄龍處理器系列中的io Die采用14nm工藝,CPU Die采用7nm工藝。在切割過程中,需要保證芯片的完整性和質量,以便后續的封裝操作。

TSV是3D封裝中的關鍵技術之一。它是穿過硅襯底的一種結構,用于實現垂直方向上不同芯片之間的信號連接。制作TSV需要精確的光刻、蝕刻等工藝。例如在HBM與下面的Die連接中,通過TSV打通硅襯底,使得信號能夠在z方向傳輸。在制作TSV時,要控制好其深寬比、孔徑大小等參數,以確保信號傳輸的質量和可靠性。

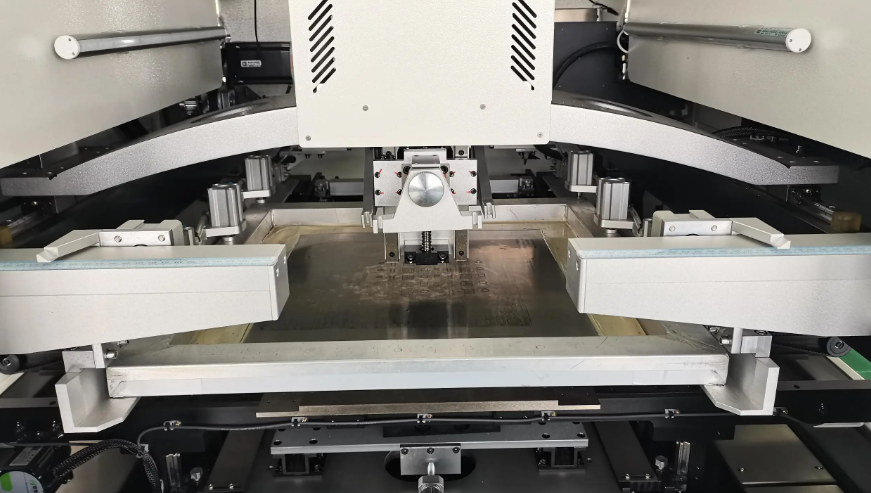

微凸塊用于連接垂直堆疊的芯片。在芯片表面制作微小的凸塊,通過這些凸塊實現上下層芯片之間的電氣連接。在堆疊過程中,要保證微凸塊與對應的連接點精確對準,這需要高精度的芯片貼裝設備和工藝。例如在3D封裝結構中,HBM的Die和下面的Die就是通過微凸塊不斷往上堆疊多層的。

RDL用于在水平方向(xy方向)上調整信號的布線。由于芯片內部不同功能模塊之間的間距(Pitch)較小,需要通過RDL將信號進行拉通,以實現芯片之間的通信。在設計RDL時,要考慮布線的長度、寬度、間距等因素,以滿足信號傳輸的高速和低延遲要求。例如在高速io、GPU、CPU或者SoC的Die之間的連通就需要RDL來進行信號的調整。

最后將堆疊好的芯片集成到封裝基板上,在這個過程中,可能會用到硅載板(Interposer)。硅載板本身也是一顆芯片,只是不含有晶體管。它可以提供更好的信號傳輸和電源分配性能,同時也有助于提高整個封裝結構的機械穩定性。例如在3D封裝結構中,下面的Interposer硅載板起到了整合所有芯片并與封裝基板連接的作用。

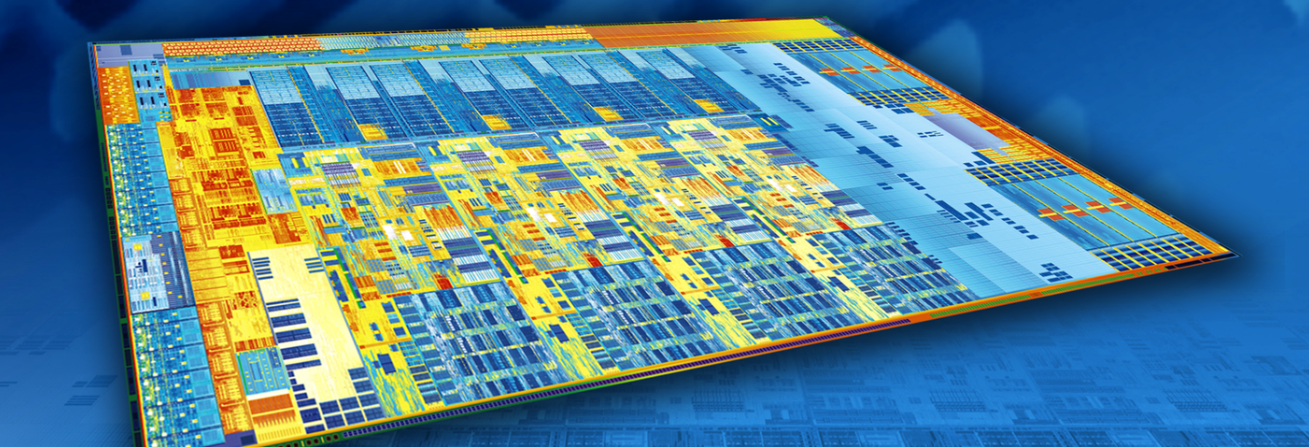

AMD的霄龍處理器系列是3D封裝技術應用的典型案例。

在這個系列中,AMD通過Chiplet技術和先進封裝技術實現了性能的質的飛躍。霄龍處理器集成了不同工藝的芯片,如io Die采用成熟的14nm工藝,CPU Die采用最新的7nm工藝。這種集成方式提高了芯片的良率,并且在成本控制上有一定優勢。

第三代霄龍產品更是集成了3D V - cache技術,在每個CPU Die上都集成了額外的Level 3的緩存(Cache),整體緩存容量超過700 MB。這一舉措顯著提升了處理器的性能,在數據中心等對性能要求極高的應用場景中表現出色。新思科技在與AMD的合作中,采用AMD最新的處理器進行測試,VCS驗證效率實現了66%以上的性能提升。并且據客戶反饋,采用AMD最新3D IC封裝的芯片,打游戲的體驗也有質的飛躍。

英特爾的Ponte Vecchio芯片也是3D封裝技術的一個成功范例。

該芯片通過5種不同的工藝將超過1000億個晶體管、47顆小芯片集成到一顆大芯片上。這種高度集成的方式展示了3D封裝技術在集成眾多小芯片方面的強大能力。通過將不同功能、不同工藝制造的小芯片集成在一起,實現了復雜的功能,滿足了高性能計算等應用的需求。

隨著技術的不斷發展,3D封裝技術將朝著更高的集成度方向發展。未來有望在一個封裝體內集成更多數量、更多種類的小芯片。例如在人工智能領域,可能會將更多的AI計算核心、不同類型的存儲芯片(如高速緩存、大容量內存等)以及專門用于數據預處理的芯片集成在一起,從而實現更強大的人工智能計算能力。這將進一步推動芯片在有限空間內實現更多功能,滿足各種復雜應用場景(如自動駕駛汽車、超級計算機等)對芯片性能和功能的高要求。

針對3D封裝散熱困難的問題,散熱技術將不斷改進。一方面,新的散熱材料可能會被研發和應用,這些材料具有更高的熱導率,能夠更有效地將芯片產生的熱量傳導出去。例如,一些新型的石墨烯基散熱材料或者高導熱陶瓷材料可能會被應用于3D封裝芯片的散熱。另一方面,散熱結構也會不斷優化。例如,設計更高效的散熱通道,采用微流道冷卻技術,通過在芯片內部或封裝結構中構建微小的冷卻液流動通道,將熱量快速帶走;或者采用3D散熱結構,如立體的散熱鰭片等,增加散熱面積,提高散熱效率。

為了應對3D封裝技術設計和制造的復雜性,相關的設計與制造技術將不斷提升。

在設計方面,會有更先進的電子設計自動化(EDA)工具出現。這些工具能夠更好地對3D封裝結構進行建模、仿真和優化,幫助工程師在設計階段就準確預測信號完整性、電源完整性、熱分布等問題,并進行合理的布局和布線。例如,能夠更精確地模擬不同層芯片之間的信號傳輸特性,優化信號路徑,減少信號干擾。

在制造方面,光刻、蝕刻、芯片堆疊等工藝技術將不斷提高精度和可靠性。例如,光刻技術可能會朝著更高分辨率、更小線寬的方向發展,從而能夠制造出更小尺寸、更高密度的TSV和微凸塊等結構。同時,芯片堆疊工藝也會更加精確和穩定,提高3D封裝的成品率。

3D封裝技術將與其他先進技術進行融合發展。

與Chiplet技術的融合將更加深入。Chiplet技術為3D封裝提供了更多可選擇的小芯片單元,3D封裝則為Chiplet提供了一種高效的集成方式。兩者相輔相成,未來將共同推動芯片架構的創新和發展。例如,通過標準化的Chiplet接口和3D封裝技術,可以更方便地實現不同來源的Chiplet集成,加速芯片的定制化和多樣化發展。

與新興的計算技術(如量子計算、神經形態計算等)結合。在量子計算領域,3D封裝技術可能用于集成量子比特(qubit)及其控制電路,提高量子芯片的集成度和性能;在神經形態計算中,3D封裝有助于將模擬神經元和突觸的電路與數字處理電路集成在一起,構建更高效的神經形態計算芯片。

先進芯片封裝清洗介紹

合明科技研發的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

水基清洗的工藝和設備配置選擇對清洗精密器件尤其重要,一旦選定,就會作為一個長期的使用和運行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環境中的濕氣,通電后發生電化學遷移,形成樹枝狀結構體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內的浮點、灰塵、塵埃等,這些污染物會導致焊點質量降低、焊接時焊點拉尖、產生氣孔、短路等等多種不良現象。

這么多污染物,到底哪些才是最備受關注的呢?助焊劑或錫膏普遍應用于回流焊和波峰焊工藝中,它們主要由溶劑、潤濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質在所有污染物中的占據主導,從產品失效情況來而言,焊后殘余物是影響產品質量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質引發接觸電阻增大,嚴重者導致開路失效,因此焊后必須進行嚴格的清洗,才能保障電路板的質量。

合明科技運用自身原創的產品技術,滿足芯片封裝工藝制程清洗的高難度技術要求,打破國外廠商在行業中的壟斷地位,為芯片封裝材料全面國產自主提供強有力的支持。

![[x]](/template/default/picture/closeimgfz1.svg)